在通信接收器中低噪声放大器(LNA)对于从噪声中析出信号十分关键。控制系统内噪声还有其他技术,包括过滤和低温冷却,但低噪声放大器的良好性能,提供了一种被实践所验证的可靠的管理通信系统噪声的方法。随之而来的是对工作于X频段(8GHz)的低功率(电池供电)LNA设计的探索。设计比较了在目标是工作于的几毫瓦DC电源的单片微波集成电路(MMIC)中,GaAs PHEMT增强型(E模式)和耗尽型(D模式)晶体管的使用。

低功率工作目标与处理不必要的(blocking)信号的应用相互矛盾。这类应用要求严格过滤和/或具有良好线性的LNA,其线性特性以三阶截止点(IP3)表示。还有,许多如全球定位系统(GPS)接收器等无线应用,可利用低功率LNA增强在没有干扰或blocking信号时的弱信号。

考虑用于LNA设计的GaAs PHEMT有两种不同的器件形式:具有典型负栅阈值电压的D模式晶体管和具有正栅阈值电压的E模式晶体管。正栅阈值电压简化了电池供电系统中的偏压。尽管有可能采用一节电池对D模式器件供电,但它需要消耗额外的流入源电阻的DC功率以满足偏压要求。

在LNA设计中,第一步是确定哪种类型器件提供最好的功能与性能的组合。下一步是选择器件的大小尺寸。器件尺寸将影响LNA的带宽、DC功耗、噪声值和非线性性能。对于一阶效应,器件尺寸不会影响增益和噪声值。然而,随着器件变得更小,匹配电路和相互联接的电阻损耗相对于器件阻抗而增加,大大增加了噪声值。

器件尺寸的选择在MMIC LNA设计中是关键的一步。漏偏电流对噪声值的影响甚至比漏偏电压的影响更大。此外,漏偏还影响放大器增益。没有足够大的电流,增益会很低。一般来说,LNA对于漏饱和电流(IDSS)偏置15%~20%,作为增益与噪声的折衷。IDSS与器件尺寸成比例,所以较大器件将比较小器件消耗更大功率。降低DC功耗的一个途径是在维持15%~20%的IDSS偏置的同时减小器件的尺寸。

降低漏电压将降低DC功耗,但器件的漏电压必须足够高以使其工作于饱和区并能够放大。除了随器件尺寸缩小噪声值增大和增益减小外,使用过小的器件还有其他缺点。包括非线性效应和由于IP3表现不佳造成的对工作带宽内干扰信号的易感性。最适合匹配50欧姆系统的器件尺寸也有一定范围。尺寸比这一优选范围小或大都趋于减少带宽,也许在窄带应用中还不太考虑,但在中等带宽应用中的确很重要。所以,尽可能缩小器件尺寸以降低功耗的直觉倾向,由于其他性能问题而有所缓和。这样,设计的功耗目标确定为毫瓦级。

一旦选定了器件尺寸、偏置电流和偏置电压,下一步是设计LNA的匹配电路。对于一般器件通常提供有非线性和线性器件模型或S参数,但它们都针特定器件尺寸,如300μm进行了优化。器件尺寸增大和缩小,误差都会随之增大,虽然我们还不清楚由于器件尺寸增大和缩小而增大的误差有多大。反复设计流程被用于开发LNA以及电路布局,并且一直要进行各种检查。最后,在将设计发出制造之前,还要进行布局设计规则检查(DRC)。

图1和图2分别显示了近乎相同的D模式和E模式LNA的布局。因为除掺杂物不同外,两种器件的GaAs制造工艺相同,只是要求匹配电路有一点点不同,以在E模式设计上优化D模式设计。虽然两种设计均针对一个偏置点进行了优化,还是要在各种电压和电流范围进行测试,以确定性能能力和DC功耗限制。

虽然两种LNA在布局上几乎一样,仿真显示在同样的DC功耗下,E模式PHEMT有更好的性能。基于计算机仿真,E模式设计比D模式PHEMT设计在1-dB压缩(P1dB)有更好的增益、噪声值和输出功率。表1对比了不同DC偏置点上的两种LNA性能。

从仿真可以看出,对于同样DC功耗E模式LNA的增益通常比D模式LNA高2dB。同样,E模式器件的噪声值通常优于D模式器件0.3dB。虽然E模式器件在1-dB压缩时提供更大的输出功率,在更高功率水平上其DC功耗增大,使这种比较显失公充。对于两种LNA的输入和输出阻抗匹配基本相同。

测量结果将显示在低功LNA设计中E模式器件性能是否优于D模式器件。为了比较结果,注意对于一块晶片样品,MMIC工艺变化可能会使两种LNA的结果有偏差。仿真基于统计上的一般器件。在PHEMT有源层(即阈值)掺杂情况变化,是可能引起两种器件性能明显变化的主要原因。所幸地,两种LNA设计中所有匹配电路和无源器件变化——微带线迹、电感和电阻都是一样的以进行比较。

在可比DC功耗水平上,基于E模式器件的LNA比基于D模式器件的LNA具有更大的增益和更好的噪声值。测量包括1-dB压缩(P1dB)的输出功率、噪声值(NF)、增益(S21)和阻抗匹配(S11, S22),结果显示于表2。

带有Cascade Microtech公司晶片探测系统的Agilent Technologies公司的HP 8510矢量网络分析仪被用于测量MMID裸片。对于两种设计,均测量了1~3V电压范围内的S参数。采用Sonnet Software公司输入和输出匹配电路软件进行的电磁(EM)仿真,与原来采用Agilent Technologies公司Advanced Design System(ADS)进行仿真相比,频率偏移稍高。实际设计的频率偏移比ADS或Sonnet的预计都高得多,这可能是由于匹配电路建模误差、PHEMT器件建模误差,或由于晶片工艺的正常变化而造成。

4x12.5μm(50μm) PHEMT是由6x50μm(300μm) PHEMT的非线性模型按比例缩放。模型按比例缩放会产生误差。较小的器件具有更高的品质系数(Q),使其更难以匹配,并且更容易由于建模或器件的变化而出现频率偏移。对一些实际的4x12.5μm D模式和E模式器件进行测量并重新仿真NLA,是确定由于PHEMT模型变化产生多大偏移的一个很好的途径。不幸的是,唯一一个可在晶片制造中测量的PHEMT为标准6x50μm器件。图3显示了采用ADS微带产品对D模式LNA进行的ADS仿真,以及采用Sonnet EM仿真的匹配电路和测量所得增益。增益比E模式LNA高大约3dB(图4)。

实际器件与预计相比,噪声值表现也在频率上有更高的偏移。对线缆损耗进行修正后,测得的噪声值比预计的高1dB左右。E模式器件表现的噪声值(及增益)出优于D模式器件。图5显示了采用噪声分析仪测得的D模式和E模式LNA的增益和噪声值。

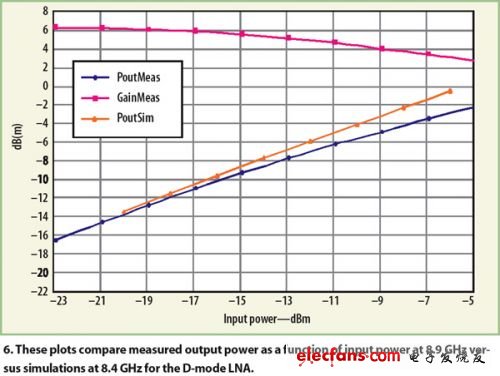

对两种器件采用信号发生器和频谱分析仪测量输出功率压缩。由于放大器比仿真在频率上有更大的偏移,原来在8.4GHz的预测值与在8.9GHz的实测值相当。图6显示了实测和仿真D模式LNA输出功率作为输入功率以及增益的函数。图7显示了E模式LNA的输出功率和增益测量。两种器件在都倾向于比仿真预测在更低输出功率上压缩。这对于在同样晶片上运行的其他设计很典型,它可能是由于正常工艺变化或建模误差造成的。

总之,D模式和E模式LNA有显示了超低DC功耗水平的优良性能。在漏电流(IDS)为2mA时,在1.0、1.5、2.0和3.0V分对的具有良好噪声性能和增益的两种设计测量其S参数。当然,输出功率在较低电压和DC功耗方面更受局限。测量2mA偏置电流3V时输出功率以进行比较。正如预计的,平均而言E模式PHEMT器件比D模式器件的增益高2~3dB,噪声值更优0.33dB。E模式器件的正栅偏压使其更容易被集成于电池供电的低功率器件中。相反,D模式器件需要负栅源电压(VGS),它要求额外的负电源或使用源电阻和更高的漏电压,以将设计转换为单一的正电源。

概括而言,TriQuint Semiconductor公司作为测试电路制造了两种类似的LNA设计,以及2005 Johns Hopkins University(JHU) MMIC Design Course(EE787)秋季课程其他学生的MMIC。两种设计以mW级的低功耗,展示了良好的增益(8~12dB)和良好的噪声值(3~3.5dB),对于低功率LNA,E模式器件展示了好得多的增益和噪声值。