为基于VPX的PCIe系统做一个异步时钟

摘要: 本设计用PCIe的VITA46.4在一个VPX系统中的外设卡和主控制器之间传送数据。它采用了PCIeRevision1,工作速度为2.5Gbps。

Abstract:

Key words :

VITA46 VPX标准定义了一种通用尺寸的机箱,它可以容纳各种形式的卡(参考文献1)。这些卡插到一个通用背板上。本设计用PCIe的VITA46.4在一个VPX系统中的外设卡和主控制器之间传送数据。它采用了PCIe Revision 1,工作速度为2.5Gbps。所有符合VPX的卡都必须使用自己的独立时钟,这与其它符合PCIe要求的系统不同,如PC。VPX外设卡也必须为PCIe事务建立自己的时钟,这意味着,时钟与主单板机是相位无关的。因此,外设时钟是异步时钟。PCIe标准允许这种情况,而对所有异步PCIe时钟有严格的抖动容差要求。

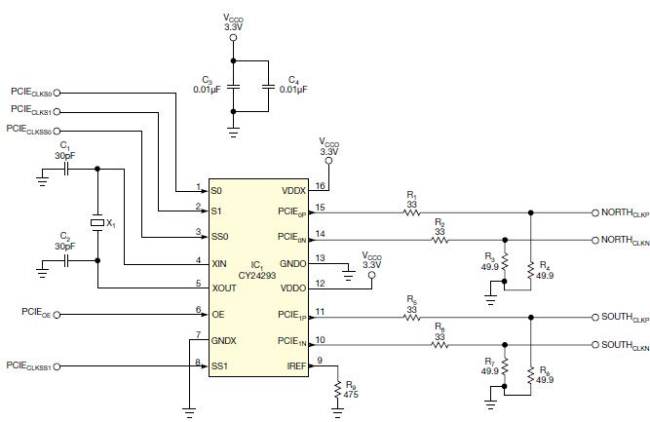

本设计中的外设卡使用了一片FPGA作为数字处理主器件。FPGA供应商的评估板通常采用PCIe接口,但板上不使用异步时钟。为了实现异步时钟, 可以用一只与某种型号振荡晶体精确匹配的时钟芯片(图1)。时钟芯片IC对晶体有抖动、老化和阻抗方面的要求。晶体应在-40°C~+85°C的温度区间内保证这些要求。必须使用CY24293数据表中的公式计算晶体的负载电容值。来自CY24293的时钟被直接送入FPGA的高速收发器时钟引脚,从而获得了外设卡与单板机之间可靠的PCIe分组传输。CY24293还有一些其它的元件与布局要求,它采用一种PCIe设备走线配置,要求有阻抗可控的特殊长度走线,以及特殊值的串联电阻。

图1,本电路将一个时钟发生器输出送至FPGA,获得一个异步VPX时钟

此内容为AET网站原创,未经授权禁止转载。