作者:Maxim公司

ADC的主要趋势之一是分辨率越来越高。这一趋势影响各种应用,包括工厂自动化、温度检测和数据采集。对更高分辨率的需求正促使设计者从传统的12位逐次逼近寄存器(SAR)ADC转至分辨率高达24位的Δ-ΣADC。

所有的ADC都会具有一定的噪声,这包括输入参考噪声(ADC固有噪声)和量化噪声(ADC转换时产生的噪声)。诸如噪声、ENOB(有效位数)、有效分辨率和无噪声分辨率等指标在很大程度上定义了ADC的实际精度。所以,理解与噪声相关的性能指标是从SAR过渡至Δ-ΣADC最困难的方面之一。由于当前对更高分辨率的迫切需求,设计者必须更好地理解ADC噪声、ENOB、有效分辨率,以及信噪比(SNR)。本文的目的正基于此。

Δ-ΣADC的更高分辨率和价值

在过去,12位SAR ADC通常足以满足各种信号和电压输入的测量。如果应用中需要更为精细的测量,可在ADC之前增加增益级或可编程增益放大器(PGA)。

分辨率为16位时,设计者的选择仍然主要是SAR ADC,但也包括部分Δ-ΣADC。然而,对于需要16位以上分辨率的设计,Δ-ΣADC则更为普遍。SAR ADC目前受限于18位,而Δ-ΣADC则延伸至18、20和24位。Δ-ΣADC还有其它优势。其价格在过去10年中已大幅下降,使用越来越简单,已被广泛接受。

有效分辨率

有效分辨率由下式定义(以位为单位):

有效分辨率= log2 [满幅输入电压范围/ADC RMS噪声]

或更为简单:

有效分辨率= log2 [VIN/VRMS NOISE]

切勿将有效分辨率与ENOB相混淆,尽管两者听起来非常类似。测量ENOB的最常见方法是对ADC的正弦波输入进行FFT分析。IEEE(r)标准1057将ENOB定义为:

ENOB = log2 [满幅输入电压范围/(ADC RMS噪声× √12)]

SINAD定义为信噪比加失真比。SINAD和ENOB用于衡量ADC的动态性能。

所以:

SINAD = [RMS输入电压/RMS噪声电压]

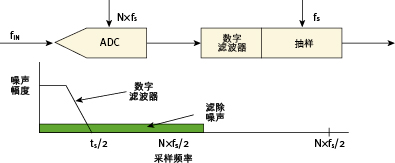

式中,RMS噪声= 1/M[eq1。

式中,EAVM =剩余XAVM,XAVM(FM)为DFT之后规定离散频率下的平均幅度谱分量。

有效分辨率和无噪声分辨率本质上衡量ADC在直流下的噪声性能,此时频谱失真(THD、SFDR)无关紧要。

知道ADC的噪声和输入范围后,计算有效分辨率和无噪声分辨率就很简单。

ADC的输入电压范围基于参考电压。如果ADC集成PGA,也会影响电压范围。有些Δ-ΣADC包括PGA,以放大小信号。最新带PGA的ADC往往规定噪声小于100nVRMS。尽管这些噪声系数与旧式ADC相比看起来很吸引人,但往往基于非常小的输入范围。这是因为小的输入范围最终会放大至适合更宽、基于参考电压的ADC有效范围。所以,尽管这些带PGA的ADC的噪声看起来很小,但有效分辨率和无噪声分辨率可能并不像无PGA的ADC那么好。

简单举例说明。PGA设置为128的24位ADC,参考电压为2.5V,输入范围为(VREF/PGA ((2.5V/128 = 39.1mV)时,噪声为70nVRMS。因此,有效分辨率为:

log2 [VIN/VRMS NOISE] = log2 [39.1mV/70nV] = 19.1位

使用相同的ADC,PGA设置为1时,噪声上升至1.53(VRMS。输入范围为5V ((2.5V/1)时,有效分辨率变为21.6位。

最佳方法是参阅ADC的数据资料,检查您所需的输入范围。

无噪声分辨率

无噪声分辨率采用峰-峰电压噪声,而非RMS噪声。无噪声分辨率由下式定义,单位也为位:

无噪声分辨率= log2 [满幅输入电压范围/ADC峰-峰噪声]

无噪声分辨率= log2 [VIN/VP-P NOISE]。

无噪声分辨率有时候也称为无闪烁分辨率。以实验室中的51/2或61/2数字多用表为例考虑这一指标。如果显示屏上的最后一位稳定且无闪烁,数据输出字则优于系统的噪声水平。

以波峰因子6.6为例,峰-峰噪声为RMS噪声的6.6倍。因此,有效分辨率比无噪声分辨率高2.7位。采用以上相同的噪声和参考值,无噪声分辨率为18.9位。

无噪声计数

无噪声计数是高精度系统的另一指标,用于评估ADC性能。对于那些可能需要50,000个无噪声计数的应用,例如电子秤,尤其如此。可将无噪声分辨率乘以系数2N,通过转换计算得到该值。

以10位ADC为例。采用210,理想10位ADC的无噪声计数为1,024。理想12位ADC的无噪声字数为4,096。同理,采用以上相同的无噪声分辨率,得到的无噪声计数为218.9或489,178。

Δ-ΣADC过采样

Δ-ΣADC的优势之一是其过采样架构。这意味着内部振荡器/时钟的工作频率远高于输出数据速率(也称为吞吐率)。有些Δ-ΣADC可改变输出数据速率。这样设计者可将采样优化为速度较高、噪声性能较差;或者优化为速度较低并带更多滤波、噪声整形(将噪声移至感兴趣测量区域之外的频带)及噪声性能更好。许多最新的Δ-ΣADC以表格形式提供有效分辨率和无噪声分辨率结果,很容易比较优缺点。

表1所示为示例ADC在双极性输入模式和单极性模式下的数据率、噪声、无噪声分辨率(NFR)和有效分辨率。ADC为MAX11200,24位器件,能够测量双极性((VREF)或单极性(0V至VREF)输入。MAX11200工作于2.7V至3.6V单电源,基准可最大偏置至电源。双极性值基于最大输入范围±3.6V;单极性测量基于0V至3.6V输入范围。

MAX11200的内部振荡器可由软件设置为2.4576MHz,在较低数据率下可提供60Hz抑制;或者设置为2.048MHz,在较低数据率下可提供50Hz抑制。无论哪种数据率,ADC噪声相同。因此,无噪声分辨率和有效分辨率值相一致。可施加外部振荡器,实现55Hz限波,很好地抑制50Hz和60Hz。

表1中详细列出的一项关键因素是双极性有效分辨率。由于输出数据字长度为24位,所以该指标限制为最大24位。在3组最低数据率设置下,如果ADC在串行接口上可输出超过24位的话,那么ADC的噪声水平可低至使有效分辨率优于24位。

有效分辨率总比无噪声分辨率好2.7位,除非受限于数据输出字。

表1. MAX11200采样率与噪声关系表。

噪声整形和滤波,实现更低噪声和更优分辨率

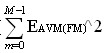

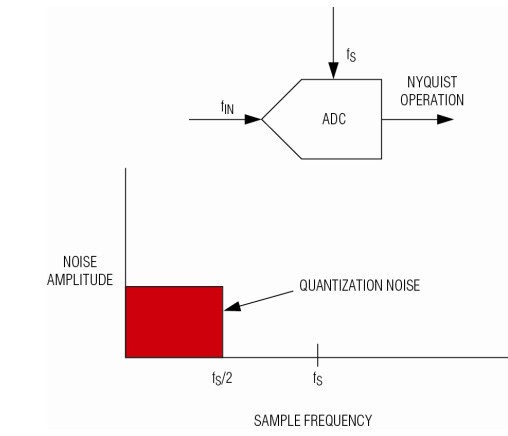

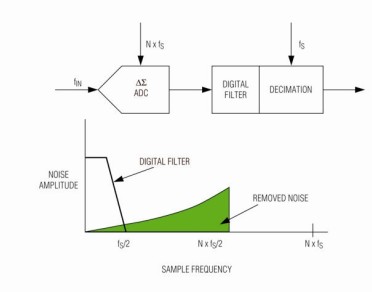

除过采样外,噪声整形可使Δ-ΣADC实现表1所示的低噪声和高精度。如图1至3所示。图1所示为标准ADC的量化噪声。图2给出的ADC包括过采样、数字滤波和抽样。采用过采样的大部分ADC核心为Δ-Σ。过采样N倍将噪声延展至更宽的频带,而数字(sinc)滤波器滤除了相当部分的噪声。

图1. 标准ADC噪声性能

图2. ADC采用N倍过采样、数字滤波器和抽样。

图3给出的Δ-Σ调制器与图2具有相同的框图,再加上噪声整形。通过将噪声不均匀地移至较高频率,感兴趣频带内的噪声变得极低。这样的技术使得Δ-Σ ADC制造商可以获得小于1(VRMS的噪声系数。

图3. ADC采用N倍过采样、噪声整形、数字滤波器和抽样。感兴趣的ADC输入频带内的噪声(绿色区域)变得非常小。

结论

Δ-ΣADC具有过采样能力和固有的低噪声,是需要较高分辨率系统设计中的极佳选择。由于设计者必须处理更小的信号,所以充分理解ADC噪声、有效分辨率、ENOB和无噪声分辨率就成为选择正确ADC方案中不可缺少的一部分。