1前言

软件无线电(Software Radio)是随着计算机技术和高速数字信号处理技术的发展迅速而发展起来的。其基本思想是将宽带A/D及D/A变换器尽可能地靠近天线,将电台的各种功能用一个开放性、模块化平台上的软件实现。软件无线电的出现使得无线电技术由以硬件为主的时代走向了以软件为主的时代。事实上,它是继模拟通信技术、数字通信技术之后的第三代无线通信技术。

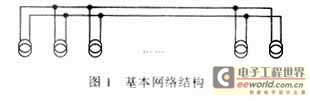

现代通信无论是有线还是无线,一般都采用集中交换方式在用户间通过交换和传输来实现点对点或点对多点的通信,但在有些特殊环境下,分布式交换系统在安全和可靠性方面独具魅力。本文论述的通信系统就是基于这种思想设计的。该数字通信系统在蜂窝移动电话通信的基础上将FDM/FDMA,TDMA、程控交换、信道扫描和分配等技术综合为一体,因而是一种全新的有线通信产品。它不需要中央控制交换机,即可在同一对馈线上实现多对用户的自动交换和通话。所有用户终端都是基于分布智能原理而实现的,即每一用户都有通信接入/撤除的支配权。因而,该系统具有广泛的应用前景。图1为该系统的基本网络结构图。

2通信终端的线路接口设计

2.1通信终端的基本功能介绍

通信终端是网络上的主要设备,每一通信电话都有接入和拆除的主动权。同时不影响其它设备的正常工作。通信终端可实现语音、数据、传真等多种业务接入。

通信终端的主要技术是软件技术,即利用DSP和MPU等先进技术,并通过软件来实现尽可能多的硬件工作,从而使设备的可靠性和灵活性大大提高,其通信终端的基本功能框图如图2所示。其中的DSP模块可实现信道扫描、自适应均衡、调制解调、信道滤波、纠错和加密、数据适配和功率控制等功能。系统管理和控制 MPU模块则可用来实现信令管理、数据接口、系统状态管理等功能。语音处理接口模块的作用是进行语音压缩处理。数据接口模块可实现与RS232接口的电平适配。系统中的供电系统包括DC/DC转换和电压监视等。

由于本系统的通信信道是某特殊双绞线,衰减率约20dB/km,因此,在信号传输10km以上时,会产生近100dB的衰减,因此,通信信道将变得非常恶劣。但它的信道幅频特性衰减比较小,并主要分布在中频。

上述的信道特点决定了该数字通信系统终端线路特殊的接口电路设计。

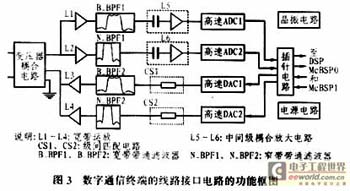

2.2数字通信终端的线路接口

由于该数字通信系统终端采用的是实时全双工通信,因此其接口电路必须具有收发两个通道。另外,该通信系统采用的是共路信令,因此其信令信道和话音信道是分开的,它们之间存在一定的保护带。所以,线路接口电路主要由信令的两路收发通道和话音的两路收发通道组成。图3所示是该数字通信终端接口电路的功能框图。图中,从变压器耦合电路进来的信号经L1→B_BPF1→L5→ADC1和从插针电路进来的信号经DAC1→CS1→B_BPF2→L3分别组成话音信道的收发通道;而从变压器耦合电路进来的信号经L2→N_BPF1→L6→ADC2和从插针电路进来的信号经 DAC2→CS2→N_BPF2→L4则分别组成了信令信道的收发通道。

3通信终端线路接口的实现

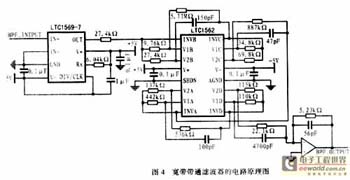

3.1宽带带通滤波电路

由于信道的衰减很大(20dB/km),因此在传输距离较长(如达到 4km)时,信号在到达接收机输入端时将有很大(80dB)的衰减,这样,信号将被淹没在噪声中,故须用一个阻带衰减至少为60dB的带通滤波器来滤除带外噪声,以提高输入信噪比(SNR),从而减小后面软件处理(信道均衡、上下统采用的是共路分开的,因此,信邻信道干扰),同扰,因此,必须分别用两个不同带宽的带通滤波器将它们分别从信道中取出,这两个滤波器的作用除了滤除带外噪声外,也可同时抑制相邻信道信号的干扰,以提高各自的输入信噪比(SINR)。此外,ADC对模拟信号的采样将使信号的频谱产生周期拓延,故须用带通滤波器对话音和信令信号的频谱加以限制以使拓延后的信号频谱不会发生混叠,同时,滤波器也可起到防混叠的作用。

本系统所选用的通用滤波芯片LTC1562在一片芯片内部集成了4个两阶滤波器,每个滤波器的中心频率可调范围为10kHz~150kHz。 LTC1562无需外部输入时钟,通过外接电阻和电容便可构成低通(LOWPASS)、带通(BANDPASS)和高通(HIGHPASS)滤波器,其中心频率(f0)、品质因素(Q)和增益(GAIN)可用电阻编程设置,该芯片既可采用单电源(+5V)供电,也可用双电源(±5V)供电。LTC1562以其上述特性完全可以在本系统中用来构成窄带带通滤波器(带宽为几kHz)和宽带带通滤波器的高通滤波部分,图4为宽带带通滤波器的实际电路。

低通滤波芯片LTC1569-7可工作在+5V单电源条件下,其截止频率可达300kHz,并可通过一个外接电阻改变滤波器的截止频率。该芯片内部集成了一个10阶的线性相位滤波器。由于截止频率在200kHz以上时,利用LTC1569-7构成低通滤波器具有比通用滤波器LTC1562 更好的特性,因此,本设计选用它作为低通滤波器。

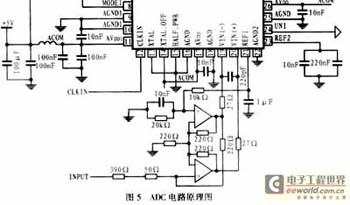

3.2 ADC的电路

虽然话音信号的带宽是位于中频部分(20kHz~200kHz),相对较宽(200kHz),但其中夹杂着大量的带内噪声,因此必须使用一个高速ADC(根据那奎斯特第一采样定理,该 ADC的采样速率必须达到500ksps,同时为了提供一定的冗余量,本系统选取的ADC芯片的最高输出采样速率也应达到1.2Msps)来将模拟信号转换为数字信号。另外,片内采用Σ-Δ调制的ADC也能对带内噪声起到良好的抑制作用,这种拟制主要通过对带内噪声整形及片内滤波器来实现,所以,高速采样 Σ-Δ调制ADC是本系统的首选。

系统中的高速ADC可选择分辨率为16位的Σ-ΔADC芯片AD7723。该器件的过采样率有 32/16×Fs可供选择(本系统采用32×Fs的过采样率)。它采用单+5V电源,片内参考为2.5V;并具有并行输出和串行输出两种方式,在输出字速率达1.2MHz的情况下,其输入信号的带宽可达 460kHz,同时能向DSP(TMS320VC5410)的McBSP提供时钟信号、帧同步信号和数据流信号,因此,该高速ADC能够和DSP组成高速数据采集系统。图5是其电路连接图。

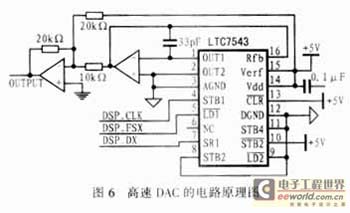

3.3 DAC电路

高速DAC可选用分辨率为12位的LTC7543,该芯片的信号转换稳定时间(settling time)典型值为0.25μs,最大值为1μs。LTC7543采用+5V单电源供电并具有和DSP(TMS320VC5410)的McBSP相兼容的时钟信号、帧同步信号和数据流信号输入引脚,输出信号可采用双极性输出,也可以采用单极性输出(本系统采用前者)。LTC7543的外围电路比较简单,图 6是其电路连接图,它由两个宽带运放,一个外部参考电压,一个电源滤波电容,一个输出滤波电容和若干电阻组成。

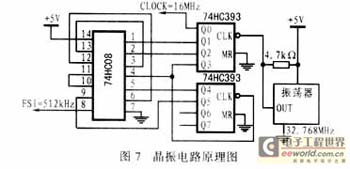

3.4晶振电路

晶振电路选用的主要器件如图7 所示,该电路包括32MHz的有源晶体振荡器、74HC393二进制分频器和74HC08逻辑与门。其中 74HC393用来产生高速ADC的时钟输入信号和帧同步信号;74HC08用来调整帧同步信号的脉宽,以使其与时钟信号的脉宽大小一致。

4结束语

以上所选的主要器件组成的电路均已做成PCB(印刷电路板),并通过信号测试。测试结果表明:窄带带通滤波器(N_BPF1、N_BPF2)的阻带衰减为 40dB;宽带带通滤波器(B_BPF1、B_BPF2)的阻带衰减为60dB;同时通过高速ADC完全可以实现对500kHz模拟信号的采样、量化和编码。