基于TMS320C5409的语音实时变速系统设计

摘要: 本文介绍的就是一种基于TMS320C5409的语音实时变速系统。另外,考虑到在实际系统中语音的压缩存储和语音变速往往是同时需求的,因此本文提出一种基于LPC低比特率语音编码算法的语音变速算法,该算法能够任意调整语音语速。

Abstract:

Key words :

在外语多媒体教学中,要求对语速进行快慢控制,以适应不同程度学生的需求。然而,传统的title="语音">语音变速产品往往在教师改变语速的同时,也改变了原说话者的语调,不能达到教学的真正目的。因此,语音变速系统应当具备调整语速的同时,还需要保证原说话者语调保持不变的特点。本文介绍的就是一种基于TMS320C5409的语音实时变速系统。另外,考虑到在实际系统中语音的压缩存储和语音变速往往是同时需求的,因此本文提出一种基于LPC低比特率语音编码算法的语音变速算法,该算法能够任意调整语音语速。

LPC算法

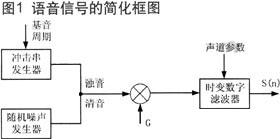

LPC编码将语音信号s(n)看作一个时变的声道系统在声门的激励之下的输出信号。对浊音而言,声门激励为一周期脉冲串;而对清音而言,声门激励为随机噪声序列。语音信号的简化框图如图1所示。

在LPC编码中,可以将一帧的语音信号用简化模型的参数来表示,如浊音、清音判别,基音周期,增益G以及数字滤波器系数{a1},这样就可以获得3kb/s的编码。解码时,由于在LPC编码中,浊音可以看作是一周期脉冲串的激励,其中,脉冲周期为基音周期,因此,为了改变语音的速率,我们将语音的帧长变长,在其中再加入若干的脉冲串的激励即可得到变速的语音信号。

硬件系统设计

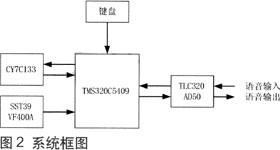

本系统是一个完善的应用系统,主要完成对语音信号的实时LPC编解码及语音变速,此外,还具有键盘控制功能和语音录放功能。因此,本系统不但需要外部的SRAM存放语音数据,而且需要与DSP相连接的键盘控制设备。本系统主要由TMS320C5409、TLC320AD50、SST39VF400A和CY7C133等构成,系统框图如图2所示。TMS320C5409内部提供的32K字片内RAM用来存放实时运行的程序和数据,片外SRAM(CY7C133)用于存放编码后的语音数据。系统的工作过程如下:系统加电后,通过复位建使TMS320C5409复位。TMS320C5409复位后,由内部固化的自引导程序将Flash(SST39VF400A)上的程序和初始化数据搬移到片内RAM,然后TMS320C5409根据键盘的控制执行操作,运行LPC编码运算(录音)、LPC解码和语音变速(放音),调整语音变速速率。

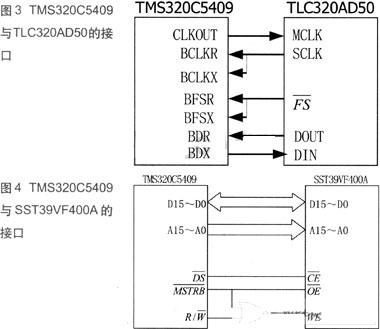

TMS320C5409用于实现语音的编解码算法,TLC320AD50用于完成语音信号的数/模和模/数转换功能。TMS320C5409与TLC320AD50之间通过McBSP串口通信。为了减轻CPU的负担,本系统中设计McBSP通过DMA收到或发送完一组单元后,再给CPU中断的方式跟CPU通信。TMS320C5409与TLC320AD50的接口如图3所示。

采用DMA的方式,即串口每收到或发送一组单元,都会自动触发DMA将其搬送到一个内部的Buffer中,等Buffer满了再通过中断方式告诉CPU处理。这时DMA最好采用ABU(Auto Buffering)模式,可以有效防止Buffer中的数据在串口速率较高时被新数据冲掉的问题。在进行语音变速时,只需要将13MA通道的帧长做相应的改变即可。

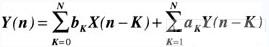

SST39VF400A(256K×1 6位)作为TMS320C5409的外部数据存储器,地址总线和数据总线接至TMS320C5409的外部总线,CR接至TMS320C5409的DS。TMS320C5409与SST39VF400A的接口如图4所示。

外部存储器采用的是CY7C133,它是高速的2K×16bit的静态异步双端口RAM,其存储速度为25ns。它有两套独立的地址线、数据线和控制信号线,允许两个控制器件中的数据通过共同连接的存储器来进行通信。该双端口RAM允许两个控制器同时读取任何存储单元(包括同时读同一单元),但不允许同时写或者一读一写统一地址单元。

对于TMS 320VC5402,数据存储器CY7C133的对应地址为4000H~47FFH。

系统软件

本系统实现的目标是键盘控制功能和语音录放功能,并且能够将输入的语音信号以任意变速率播放而不改变语音的声调。系统采用C语言进行功能开发。

本系统中将HPI口映射成为GPIO,并且将键盘连线通过"或"门接到INTO。当有按键按下时,INTO中断处理程序通过从GPIO中读出的数值判断此时是录音、放音、语速变快还是语速变慢。

抗干扰设计

本系统中既采用硬件抗干扰技术,也采用了软件抗干扰技术。下面简要介绍一下本系统所采用的硬件看门狗和数字滤波器的设计。

利用硬件看门狗功能提高系统的抗干扰能力。由专用芯片MAX692构成的看门狗电路(图5),系统所用外围元件少。MAX692是微系统监控电路芯片,具有后备电池切换、掉电判别、看门狗监控等功能。其中WDI是看门狗检测输入端,接到数字电路系统的一个专用I/O口或一个总线口上。RESET是复位信号输出端,接数字电路系统的复位端RST。MAX692的WDI定时周期为1.6 s,复位脉冲宽度是200ms。如果WDI保持高或低超过"看门狗"定时周期(1.6s),RESET端将发生200ms宽(最小140ms)的负脉冲使数字电路系统复位。

设数字滤波器的输入信号为X(n),输出信号为Y(n),则输入序列和输出序列之间的关系可用差分方程表示为:

式中输入信号X(n)可以是语音信号经采样和ADC变换后得到的数字序列,也可以是计算机的输出信号;aK和bK均为系数,通过设置aK和bK可将DF设计成需要的带通滤波器。

数字滤波器的软件设计方法有:程序判断滤波法(限幅滤波法)、中位值滤波法、算术平均滤波法、递推平均滤波法、防脉冲干扰平均滤波法、一阶滞后滤波法等6种方法。根据需要,本系统选择程序判断滤波法。

结浯

实践证明,本系统在进行语音变速的同时,能够保证原说话者语调保持不变,且操作简单,系统延时小。

此内容为AET网站原创,未经授权禁止转载。