XILINX在Transceiver用户手册里提出了对模拟电源的文波噪声要求:10mV p-p 10kHz~80Mhz。大多数客户一看到该指标要求的第一反应是——我做不到,XILINX的Tran

事实是这样的吗?不是。XILINX在其用户手册里给出该指标,是为了方便客户作电源设计。因为,有数据可

随着Transceiver的工作速率越来越高,通道数越来越多,需要的电源电流越来越大。原来的LDO+

XILINX给出10mV p-p 10kHz~80Mhz的指标是有依据的,可实现的。XILINX最早在UG366里给出该指标时做过电

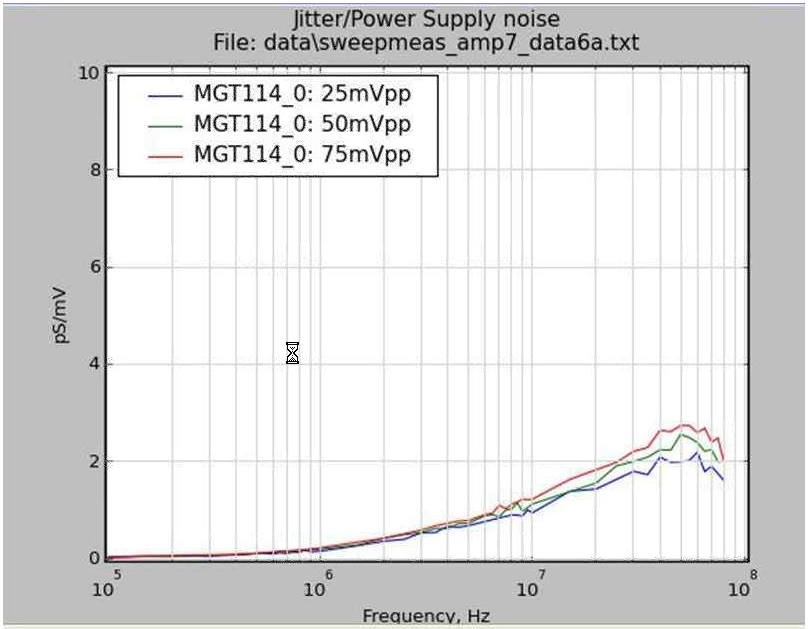

图1 电源文波噪声到输出Jitter的传递函数曲线

可见,随着频率的升高,每毫伏产生的输出Jitter增加。在10MHz时的灵敏度大约是1.5pS/mV

图2.在不同频点注入0.4UI的Jitter的CDR 抖动容忍度曲线

图3. 在10MHz频点注入不同Jitter的CDR 抖动容忍度曲线

但是,对于电源测试来说,10mV p-p 10kHz~80Mhz的指标确实是挑战。很多仪表(示波器)的本底噪声可能已经接近5mV,如果探头系

图4 长余辉法测试电源噪声

图5 频谱仪法测试电源噪声谱

从最近几年的工程实践来看,即使是没有使用单独的DC/DC模块给SERDES供电,也没有引起SERDE