一、方案设计基础

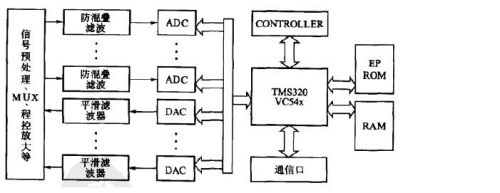

DSP方案设计包括硬件设计以及软件设计两部分。硬件设计又称为目标板设计,是基于算法需求分析、成本、体积、功耗等全面考虑的基础上完成的设计,如图1-1是一个典型的DSP目标板结构图。

图1-1 DSP目标板

二、数字电台原理设计

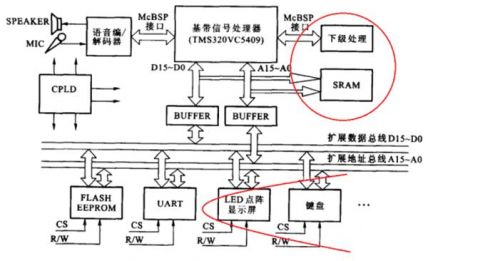

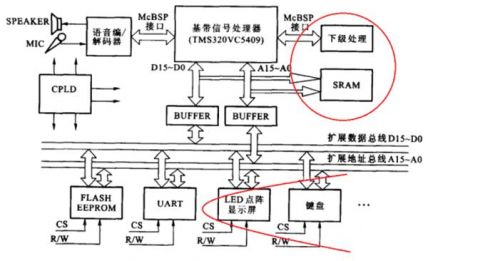

采用CVSD(连续可变斜率增量调制)语音编解码和UART数据接口,送入基带处理模块的语音数据流最高为16kbps,数据流最高为9.6kbps,DSP的基带处理,包括进行信道编/译码、加入/提取信令、组/拆帧等,送出64kbps数据到数字调制/解调电路。

图1-2

对于数字语音通信,从MIC(话筒)来的语音信号在语音编解码器中,经过CVSD编码变为16kbps串行数字语音流。通过VC5409的一个多通道缓冲串口(McBSP)接收引脚送入,再进行信道编码,以增强纠错能力。

从VC5409上引出的16位数据线(D15-D0)与16位地址线(A15-A0),经过了一级总线驱动器(BUFFER),增强驱动能力,以扩展足够的外设。

在此基带处理模块的设计中,需要扩展EEPROM存储器与通用异步收发器(UART)。扩展EEPROM是为了存储用户的数据以及编制的软件,并在目标板上电时,通过Bootloader引导DSP片内RAM,完成用户程序的自启动。扩展UART接口是针对数据通信任务,主控机或者上位机可通过UART接口与基带处理模块上的VC5409进行数据交换。

对于上图1-2,本电台基带处理系统包括7个子模块:语音前端、基带DSP、UART、BUFFER、扩展存储器、CPLD控制单元、电源。不包括下级处理模块,以及扩展的外设显示屏、键盘等。

三、设计中每部分的作用

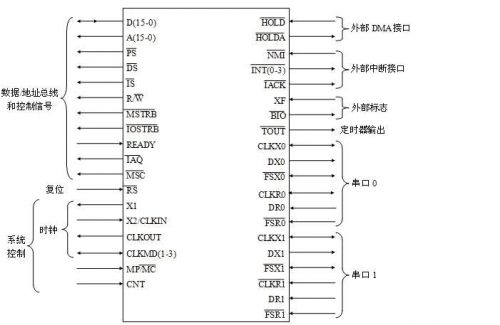

1、基带DSP

TMS320VC5409芯片主要包括CPU、片内存储器和片内外设三个部分,它们通过片内总线相互连接,交换数据信息和控制信息。TMS320VC5409配置有片内RAM 32K,片内ROM 16K,三个串口,一个并口。

VC5409的三个串口使用了其中的两个,一个用于接收和发送语音编码信号,另一个用于接收和发送标准输入信号。由于DSP的串口是极其宝贵的资源,所以需要剩下一个串口通过CPLD预留出来,以备系统扩展。考虑到系统的完整性,还预留了HPI接口(HD0-HD7)。

VC5409的总线均连接到了总线驱动器SN74LVTH16245上,所有外设的地址线和数据线连接到总线驱动器的另一端,这样连接的目的是数据缓冲和隔离保护DSP芯片VC5409,避免DSP芯片被烧坏。

由于DSP芯片的程序一般是烧在存储器中的,但是这些非遗失性的存储器(ROM)访问速度较慢,一般不能直接用做程序存储器使用,需要在上电时引导到CPU的高速程序存储器中,这个过程称为BOOTLOADER。VC54xx系列DSP在片上ROM放有引导程序,使用该引导程序可以很方便的在DSP上电复位时将用户的应用程序从外部存储设备中装入到DSP片内存储器和高速片外程序存储器中。本设计是将程序烧在EPROM中的,所以采用的是EPROM并口引导方式。

2、DSP电源设计

DSP电源可以采用由TPS73HD318芯片组成的双电源电路,1.8V主要为VC5409的内部逻辑提供电压,包括CPU、时钟电路和所有外设;3.3V电压为外部接口引脚供电;它还带有200ms宽脉冲的复位信号,其中TPS-RS就是复位信号,可利用此信号使DSP、URAT复位。电源电压为12V,12V的电源电压通过稳压器7805与7905转换为5V电压。选用12V作为系统的电源电源是因为芯片MC3418需要的电压是12V,为所有芯片里面需呀供电电压最高的,而其他芯片只需5V甚至更低。

3、语音前端设计

该功能模块的主要任务是对输入的低功率语音信号进行放大滤波,转换为负载所需的足够的输出功率信号。之后需要再对语音信号进行编码。语音前端可分为信号放大滤波电路与语音编解码电路。

语音信号放大滤波电路,是为了把信号增大到可利用的程度。在语音编码前端对信号进行放大选用LM356运算放大器,其输入性能比通常的运放增强一个数量级以上,可以应用于采样和同步电路、快速的A/D和D/A转换器、宽带、低噪声等放大器。

编/解码芯片采用MC3418。这但是单片MC3418只能工作在半双工模式。为了完成全双工,采用了两片MC3418,分别用于编解码电路。

编码和解码电路的外围电路相同,编码电路将编/解码选择引脚(15脚)置高电平,解码电路将此引脚接地即处于低电平。

4、UART部分

扩展设备UART包括电平转换器和UART协议控制器。电平转换器将计算机串口送来的15v数据电平转化为0~5V的TTL电平。UART协议控制器选用的是TL160C550。

TL160C550的作用是对从外围器件接收的信号实行串行到并行的转换,对从CPU接收的信号实行并行到串行的转换。在ACE(异步通信单元)工作的任何时候CPU都可以读ACE(异步通信单元)的状态。该接口使用TL16C550芯片是TL16C450异步通信单元(ACE)的升级产品。TL16C550内嵌完整的MODEM控制协议和处理器终端系统,减轻用户在通信协议上的软件编程以及管理工作。TL16C550还有可编程的片内波特率产生器,能对基准时钟进行分频并产生内部发生器逻辑的16*时钟,DSP可以在任何时刻访问其内部寄存器。它使用1.8432MHz和3.072MHz晶体频率的波特率产生器可得到各种的数据速率。该系统把UART扩展在VC5409的I/O空间。

TL16C550输出的是TTL电平,所以在跟PC通信时需要进行电平转换,转换为RS-232电平。电平转换使用MAX3238即多通道RS-232驱动器/接收器。

6、总线驱动器

由于DSP芯片的地址总线和数据总线的驱动能力有限,从VC5409上引出的16为数据线(D15-D0)与16位地址线(A15-10),经过一级总线驱动器(BUFFER),可以有效增强驱动能力,以便扩展足够的外设。同时BUFFER起到隔离作用,避免扩展的5V高电压外设烧毁3.3V的低电压VC5409。总线驱动器器件选用SN74LVTH16245,这是一种16位总线驱动器,与地址、数据总线均为16位的VC5409匹配。其中数据总线使用SN74LVTH16245来进行双向驱动,需要特别是针对数据总线进行加强驱动能力的设计;地址总线是单向的,没有方向的控制使用SN74LVTH16245单向驱动器就可以了。

7、扩展存储器

由于VC5409为ROM型器件,用户的运行程序和数据在掉电后不能保留,需要扩展FLASH EEPROM来加以存储。