0 引言

运算放大器是许多模拟系统和混合信号系统中的一个重要部分.高的直流增益无疑是运算放大器重要的设计指标.由于运算放大器一般用来实现一个反馈系统,其开环直流增益的大小决定了使用运算放大器的反馈系统的精度.在现代CMOS模拟电路中,低压差线性稳压器(LDO)的设计中,要求运算放大器有高的直流增益来减小其静态误差.折叠式共源共栅结构可以提供高的增益,大的输出电压摆幅,好的频率特性,而且功耗比较低.

本文根据设计要求,设计了一种采用增益提高技术的两级放大器:第一级为在差分输入单端输出的折叠式共源共栅放大器中采用增益提高技术的低电压电流镜,以达到高增益且可提供适当摆幅,第二级采用共源极电路结构以增大输出摆幅,同时提供适当的增益.在放大器的两级之间,采用改善零点频率的密勒补偿技术来使电路达到稳定.经过Cadence spectre软件仿真显示,该结构直流增益达到了125.8 dB,相位裕度达到了61.2°.

1 运算放大器的设计

本文所设计的电路是在采用折叠式共源共栅结构的两级放大器中,采用增益提高技术的低电压电流镜来得到高增益.

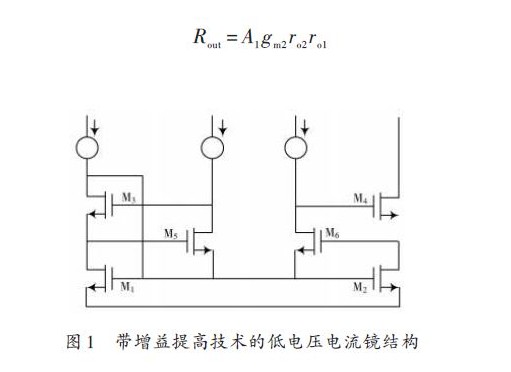

增益提高技术利用反馈技术来提高信号通路上的输出阻抗,可以通过如图1所示的结构来说明.该结构通过电流电压反馈来控制M4 源端的电压,使其保持恒定值,由于放大器M6 的作用,输出电压的变化对M2 漏端电压的影响很小.通过M2 的电流变得恒定,从而产生更高的输出阻抗.由小信号电路分析可知,该电路的输出阻抗与传统的共源共栅结构相比,增加了A1 倍.

其输出阻抗表达式为:

2 总电路结构

图2 为运算放大器的总电路结构:第一级采用PMOS管作为输入管的折叠式共源共栅结构,并且在其增益提高级采用了增益提高技术来提高输出阻抗,进而提高增益.第二级采用简单的共源级的典型结构输出,以提供最大的输出摆幅.为使电路达到稳定,在增益提高级与输出之间采用了改善零点频率的密勒补偿.

电路的静态工作条件由偏置电路提供.

2.1 输入级电路结构设计

在两级运算放大器的设计中,第一级提供高增益;而在单级放大器中,折叠式共源共栅和套筒式共源共栅均可提供很高的增益.折叠式共源共栅运放与套筒式结构相比,电压的输出摆幅较大些,而且在应用方面输入输出可以短接,实现单位增益缓冲器;其次,折叠式共源共栅结构的输入共模范围大,输入共模电平可以接近VDD(NMOS作输入管)或GND(PMOS作输入管).若采用NMOS管作为输入管,由于电子比空穴迁移率大,能得到更大的增益,但其折叠点有很大的寄生电容,影响了运放的速度,所以可采用PMOS管作为输入管来提高主放大器的频率特性.本文设计的差分输入单端输出的折叠式共源共栅结构如图3 所示,其中M1 ,M2 ,M5 ,M6 构成折叠式差分电路;M3 ,M4 构成差分电路的偏置电流源;M19 构成差分输入的尾电流源;M7 ,M8 ,M9 ,M10 构成共源共栅电路;M13 ,M14 ,M15 ,M16 ,M17 ,M18 构成增益提高电路,来提高第一级的输出电阻.

Vbias1 ,Vbias2 ,Vbias3 提供增益提高级的直流偏置电压.在第一级PMOS差分输入的折叠式共源共栅中,增益提高技术的增益为:

运放第一级的增益为:Av1 = Gm *Rout ,Gm 为输入差分管的跨导.

2.2 输出级电路结构设计

第二级采用电流源负载的共源级电路,不仅可以提供很大的电压增益,还可以提供大的输出摆幅.在本文的设计中,如图4所示,M11 作为第二级的输入管,M12管提供偏置电流,其偏置电压由Vbias3 提供.其增益为:

2.3 偏置电路结构的设计

图5 是本文所设计的偏置电路,Vbias1 为图3 中输入管的尾电流源M19 提供直流偏置电压,Vbias2 为图3中M5 ,M6 ,M7 ,M8 ,M15 ,M16 提供直流偏置电压,Vbias3 为M3 ,M4 ,M12 提供直流偏置电压.M20 ,M21 构成电流镜,理想电流源通过电流镜将电流Iref 按管子的宽长比镜像到M21 管,从而产生电路所需要的直流偏置电压.

2.4 运算放大器整体电路结构

图6 为本文所设计的运算放大器的整体电路.各个端口定义为:VDD 为工作电压;GND 为电源地;Vin1 为正相输入端;Vin2 为反相输入端;Vout 为输出端;电阻Rm=1 kΩ,电容Cm=4 pF.Iref 为10 μA 的电流源.为了使在闭环电路中反馈运算放大器的输入端的信号幅度和相位不使该信号在环路中产生振荡,在电路的增益提高级和输出级之间添加了密勒补偿电容和补偿电阻.电路的第一级为采用增益提高技术的共源共栅结构,其输出电阻很大,所以主极点在第一级的输出端.采用密勒补偿电容Cm 把主极点向低频移动,非主极点向高频移动来实现极点分离.采用补偿电阻Rm 来改善零点的频率,从而使运算放大器达到稳定.表1为整个运算放大器的各个管子的尺寸参数.

3 电路仿真结果

采用Cadence公司的仿真工具spectre,仿真模型采用Chartered 0.35 μm,3.3 V 工艺BSIM3V3 模型对所设计的运算放大器进行了仿真.增益和相位仿真结果如图7所示,增益为125.8 dB,增益带宽积为2.43 MHz,相位裕度为61.2°.

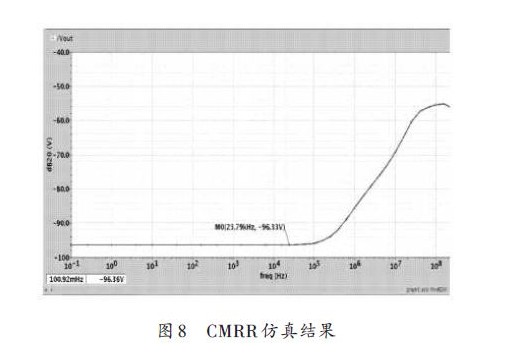

在仿真过程中,对CMRR 的仿真采用了简化的仿真办法,仿真的是实际数据的倒数.从图8 中可以看出,低频共模抑制比(CMRR)为96.3 dB.

表2 为所设计的运算放大器与其他两级运算放大器性能的比较.

4 结论

本文采用Cadence公司的仿真工具spectre,仿真模型采用chartered 0.35 μm 工艺对所设计的采用增益提高技术的折叠式共源共栅两级放大器进行了DC,AC及瞬态分析,仿真结果表明,本文所设计的两级运算放大器具有125.8 dB的直流开环增益,与采用类似技术的其他放大器相比,其增益可达到最大.在1 pF的负载电容条件下,运放的单位增益带宽积为2.43 MHz,相位裕度为61.2°,共模抑制比96.3 dB,使电路达到了稳定状态,并且模拟结果达到了预期的效果.