用作功率开关的MOSFET

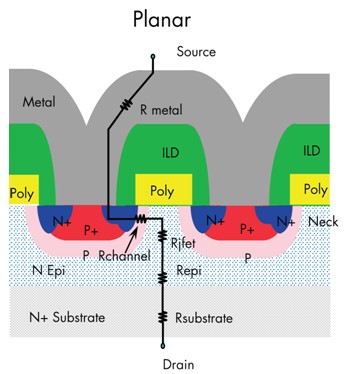

随着数十年来器件设计的不断优化,功率MOSFET晶体管带来了新的电路拓扑和电源效率的提升。功率器件从电流驱动变为电压驱动,加快了这些产品的市场渗透速度。上世纪80年代,平面栅极功率MOSFET首度面向高压器件,BVDSS电压范围达到500-600V,取得市场的成功。在这个时期,功率MOSFET的传导损耗主要取决于沟道密度、结型场效应管(JFET)阻抗和外延阻抗(参见图1)。随着半导体行业光刻设备越来越精密,提高了晶体管单元密度,传导损耗因而得以改善。光刻设备能够实现更高的单元密度,同时也促使功率MOSFET的BVDSS范围成功地下降到100V以内,实现了新的汽车电子、电源和电机控制应用。高压MOSFET的传导损耗问题也就转移到外延设计之上。另一方面,MOSFET器件在降压转换器中的使用,以及更宽的电源电压范围(30V)要求,激发了市场对更高性能器件的需求。

上世纪90年代初期平面功率MOSFET技术的长足发展之时,出现了一类新型沟道栅极功率MOSFET,为低压器件设立了新的性能标杆。这类沟道MOSFET采用一种嵌入在沟道区域并细致地蚀刻到器件的栅极结构,使得沟道密度增加一倍(第一代产品就达到每平方英寸1200万个单元)。由于新技术能够增加并行传导通道的数量并减少JFET阻抗元件,因此使到传导效率提高近30%。

器件设计人员面对的挑战是:技术提升除了增加单元密度,因为栅极-漏极区域交叠面积和栅极-源极交叠面积增加,所以同时引起容抗和栅极电荷的增加。因此,器件设计人员一直希望通过结构创新来减少开关损耗。飞兆半导体公司于1998年推出一种专为高效降压转换器而优化的沟道栅极功率MOSFET,也就是第一代PowerTrench® 产品。如今PowerTrench®已经过七代改进优化,演变为最新的降压转换器部件。

针对同步整流拓扑的功率MOSFET优化

随着首批微控制器开始使用有别于计算机的标准5V或12V电源,功率MOSFET也开始获得广泛应用。将直流电压转换成更低电压的旧式降压转换器,成为低电压开关功率器件发展的应用驱动力。而且开发焦点也从AC-DC开关电源和电机驱动,转向要求更严苛的处理器以及能满足特定的供电要求的相关外设组件。

作为处理器电源的降压转换器随即增配同步整流器以改善效率,并使用同步开关功率MOSFET来补充并最终替代肖特基整流二极管,从而降低传导损耗。而移动计算技术的出现,对转换器效率提出了更高求,进而推动了该技术的高度演进,成为现代功率MOSFET中使用的模式。

在高技术水平下,易于确定对降压转换器MOSFET的要求。在大多数情况下,同步整流器或SyncFET™都在导通状态下工作,并且其导通阻抗应当很小,以最大限度减少功耗。高侧开关MOSFET由直流电源驱动,生成电脉冲,然后经LC滤波器平滑处理成连续的电压,再施加到负载上。因为MOSFET的主要损耗来自开关动作,而且导通时间很短,所以开关器件速度要够快,而且导通阻抗要够小。开关和整流两个环节交替处于导通状态,但导通时段不能重叠,否则电源和接地间便会形成所谓直通(shoot-through),直接造成功率损耗。当开关器件导通时,SyncFET™的漏极电压瞬变将在栅极CGS上产生感应电流和电压,其大小则取决于CGS和CGD的幅度及两者的比率以及开关瞬变速率。如果栅极电压超过阈值,器件将再次导通,导致直通。所以只要CGS/CGD比率足够大,便能够防止漏极电压瞬变诱发直通。

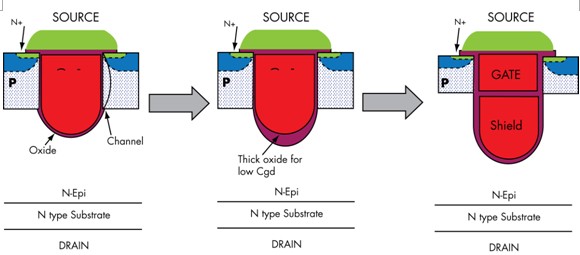

分析该技术演进并明确MOSFET要求后,就能明白器件技术发展的主要推动因素。在图2a的基本沟道栅极结构中,通过增加沟道的宽度/长度比,便可以降低导通阻抗。而按图2b所示在沟道底部延伸氧化层厚度,就能够提高开关速度和增大CGS/ CGD比率。最终的设定就如图2c所示,在沟道的栅极下部额外嵌入一个电极,以增加漂移区电荷,从而降低导通阻抗;并且同时降低CGD,提高开关速度,并改变CGS /CGD比率,藉此最大限度地防止直通。

图2:a)传统沟道栅极功率MOSFET;b)沟道底部氧化层加厚的沟道MOSFET;c)增添屏蔽电极的沟道MOSFET。

如今,飞兆半导体公司已将上述屏蔽器件的结构发展到新的精细水平。特定阻抗,或者说单位面积阻抗,已较上一代产品大幅降低,同时提高了业已出色的开关性能。过去的数代器件,例如飞兆半导体的领先产品SyncFET,也需要在低侧同步整流器集成一个肖特基二极管,以降低MOSFET体二极管的死区时间(dead-time)传导损耗,并控制体二极管反向恢复时产生的电压瞬变。为了省去成本相对高昂的肖特基二极管,最新一代的产品采用二极管正向注入,以求最大限度地减小漏极屏蔽容抗,以及降低屏蔽阻抗等专业技术,力争抑制那些不利的电压瞬变行为,如漏极电压过冲(over-shoot)。

如图3a和3b所示,新产品的电压过冲和振荡甚至大大低于采用集成肖特基部件的器件。SyncFET漏极电压振荡经过阻尼抑制,使该类应用中常见的EMI噪声大大减少。该解决方案具有极其安静的开关特性,可以完全省去用来消除振荡的外部缓冲电路。

图3:飞兆半导体器件的安静开关行为(a)与传统沟道产品开关行为(b)的比较

由于器件技术不断演进,新产品也开始百花齐放。这些产品通过降低MOSFET开关的功耗来提高性能及电压转换器的最大输出电流。目前,SyncFET通常使用三个毫欧级部件,使多相转换器的每级输出电流都达到30A以上。鉴于过去数代产品的部件之间存在封装互连阻抗,而这种互连阻抗与当今PowerTrench产品的整体阻抗相接近,相比之下,这是一项卓越的成就。封装互连阻抗降低了八倍,使过去10年来针对半导体阻抗取得四倍的改进,结果使转换器输出电流增加了一倍。新产品在未来可达到的进展还包括提高工作频率,使到滤波电感和电容更小,进而减少所用的电路板空间。

包含封装的控制器和(或)驱动电路以及功率开关的多芯片模块正在打进诸如游戏机和便携电脑之类的消费电子产品市场。这些新型部件的优势包括减少电路板的寄生电感因素、避免了分立元件方案所产生的电压瞬变,以及从转换器剥夺功率的固有弱点,从而延长电池寿命,降低工作温度,减低辐射噪声或EMI,并减小电路板尺寸。

封装和MOSFET器件技术的进步,大多来自于日益增多的仿真技术的使用,让工程师能够开发创新的解决方案。本文所述的半导体技术发展就依赖于器件的有限元模拟分析和应用的模拟分析,从而对半导体 、封装、栅极驱动电路和电路板寄生因素间的相互影响有更深入的了解。仿真技术还能让人们深入了解器件参数变化的工艺环节,找到最大限度消除这些变化的解决方案。

结论

要开发针对高级电源的先进功率器件并取得市场佳绩,必须考虑和顺应不断演进的应用需求。这需要针对应用中的所有元件进行大量的优化工作,包括功率器件的半导体芯片、封装、电路板布局,以及转换器的工作频率。飞兆半导体公司认识到这一挑战,并使用新的设计原则来开发功率MOSFET。飞兆半导体在电源设计方面拥有的专业优势,使其PowerTrench产品功能在业界稳占领先地位。