串行外围设备接口SPI(serial peripheralinterface)总线技术是MOTOROLA公司推出的一种微处理器、微控制器及其外设间的一种全/半双工同步串行数据接口标准,具有连接线少、传输效率高等特点,因其硬件功能很强,与SPI有关的软件就相当简单,使CPU有更多的时间处理其他事务。

SPI接口一般采用4条连接线:串行时钟线(SCK)、主机输出/从机输入数据线(MOSI)、主机输入/从机输出数据线(MISO)和低电平使能的从机选择线(SS),有的还带有中断信号线(INT),半双工或单向模式则不需要主机输出/从机输入数据线(MOSI)。为了在减少引脚的基础上完成主从机的双向通讯,本文采用半双工机制实现了一种3线制双向SPI总线模块,即通过使能信号实现数据传输的方向控制,因此将主机输出/从机输入(MOSI)线和主机输入/从机输出线(MISO)线合并为一条双向信号线。该模块是某射频芯片中的接口模块,其作用是实现基带芯片对射频芯片的控制以及数据交换,而且为了便于和射频电路集成,该模块最终以硬IP形式实现。

1 SPI总线协议

射频芯片的SPI接口具有两个主要特征:Slave工作模式和半双工方式通讯。

SPI接口信号描述如表1。

接口时序要求如下:

1)输出时序

当SEN为高电平时,SPI接口处于输出状态。每次数据传输开始于SCK信号的上升沿。数据传输过程中,数据由SCK信号控制,并遵循下列规则:数据传输时,低位在前,高位在后;每个输出数据位在SCK下降沿采样;当本帧数据输出达到24 bit时,结束数据输出;当本帧数据输出超过24 bit时,则多余位数全为高电平。

2)输入时序

当SEN为低电平时,SPI接口处于输入状态。每次数据传输开始于SEN信号的下降沿,结束于其上升沿。数据传输过程中命令和数据有SCK和SEN信号控制,并遵循下列规则:数据传输时,低位在前,高位在后;每个输入数据在SCK下降沿移入MOSI;当本帧数据输入为24 bit时,当SEN转为高电平时,将已输入的24 bit数据写入RF IC内部寄存器;当本帧数据输入不足24 bit或多于24 bit时,放弃本帧输入,等待下一帧。

射频SPI接口的最大特点就是采用半双工通讯机制,串行数据的输入/输出共用一条数据线,因此SPI接口数据通路的设计和普通的4线制SPI接口完全不同。

2 实现方案

2.1 总体结构

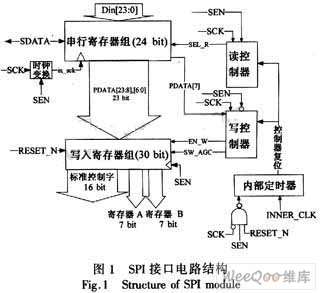

SPI接口电路主要由读/写控制器、串行寄存器组、输出寄存器组和内部定时器四部分构成,如图1所示。

在SPI接口模块中,数据交换的核心是串行寄存器组,读、写控制器根据外部方向选择信号SEN交替控制串行寄存器组的输人和输出。

2.2 串行寄存器组

串行寄存器的作用是接收射频芯片内部状态信息并转换成24 bit串行数据输出,以及接收外部串行控制字输入并转换成30 bit并行数据输入射频芯片,其基本结构如图2所示。串行寄存器组是半双工方式SPI接口设计的核心,输入和输出数据共享此数据通路,必须保证数据传输方向的正确切换。本文采用串行寄存器链+输入选择器方式实现输入和输出数据间的切换。

2.3 读控制器

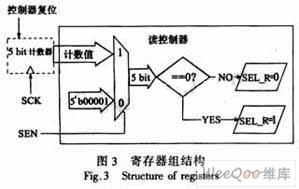

读控制器的作用是在SEN为高电平的周期内,控制串行寄存器组在第一个SCK上升沿到来时接收指定的24 bit射频芯片内部信号,并将最低位串行输出,然后在剩下的23个时钟周期内将余下的23 bit数据串行输出,读控制器结构如图3所示。

2.4 写入寄存器组

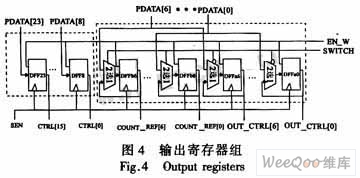

写入寄存器的作用是在SEN信号的上升沿接收串行寄存器组的输出,并将结果写入射频芯片的内部模块。其中射频芯片比较特殊的要求是根据写入控制字第7位选择将串行输入数据的第0~6 bit数据写入两个不同的控制寄存器中的一个,这样,写入寄存器组的输出位数就变成了30 bit,输入为23 bit。输出寄存器的结构如图4所示。

2.5 写控制器

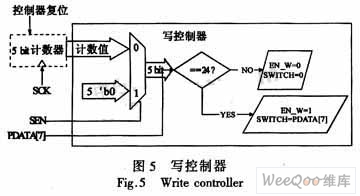

写控制器的作用是在SEN信号的低电平周期内,判断写入数据是否恰好满足24 bit以使能输出寄存器组,另外根据写入数据的第8位控制低7位数据的写入方向(寄存器A或寄存器B)。写控制器的结构如图5所示。

3 实现结果

图6是采用Verilos实现的SPI接口的部分功能仿真波形,测试激励首先将SPI接口置于发送模式下(SEN为高电平),SPI接口将从内部获得的信息码“24’hFFFFFE”正确地串行发出;测试激励再将SPI接口置于接收模式下(SEN为低电平),SPI接口正确接收外部发送的“24’hFFFFF8”,并转换成内部的“30’h3FFC078”。为了保证收发方向切换在一个时钟周期内完成,SEN信号的转换在接口时钟的下降沿完成。通过NC-Verilog仿真,SPI接口功能正确,工作时序符合设计要求。

4 结论

本SPI接口模块已成功应用在一个射频芯片中,以硬IP的形式集成进射频模块中。SPI接口电路在0.18 μm工艺下实现后的版图总尺寸约为240 μm×460 μm,最高工作频率原高于10 MHz的设计上限,相应在10 MHz下的功耗约为2 mW。