文献标识码: A

文章编号: 0258-7998(2015)04-0046-04

0 引言

LED作为一种新型光源,以其低供电电压、低功耗、长寿命、无辐射等特点被广泛应用于各种场合。

LED本身的发光特性使其具有易控制、频闪快的特点。因此把三基色的LED驱动电路做成专用集成电路(ASIC),按PWM(占空比)方式独立控制R(红)、G(绿)、B(蓝)三种LED的发光灰度就可实现全彩效果的LED灯光控制技术。这样既可以大大地简化整个LED应用系统的复杂度,又降低LED系统产品的成本,同时提高LED产品的可靠性[1]。

本文提出了一个三通道LED恒压驱动控制专用器件的ASIC设计方案,驱动IC内部集成数字接口、数据锁存器及脉冲宽度调制(PWM)等模块电路。通过外围控制器和简单的应用电路就可实现该驱动芯片对LED的单独灰度控制。同时,驱动芯片采用数据自动整形转发技术。这样在具体工程应用中可以将驱动芯片进行单线级联,且级联个数不受信号传送的限制而仅仅受限刷屏技术要求。该方案简化了工程应用电路,同时使得图像的更新速度满足了视觉无闪烁的要求。

1 设计思路

本文设计的三通道LED驱动芯片采用单极性归零码的方式收发数据,在具体工程应用中可以以500 kb/s(低速)或者1 Mb/s(高速)的速度接收控制器发出的视觉数据信号。

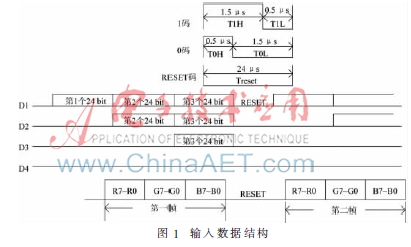

芯片可接收的单极性归零码数据形式如图1所示。这种码型中每个比特位都有归零措施,从而降低了低频成分,有利于信号的传输。同时在每个比特位的开始时刻都存在由低电位到高电位的跳变,含有丰富的定时信息。同时1/4和3/4的占空比的编码方式使得芯片的解码更准确。应用这样的编解码方式可允许芯片存在一定的采样时钟偏差。如图1所示,低速模式下该码型以占空比3/4、周期为1.5 ?滋s的矩形脉冲表示“1”,以占空比1/4、周期为0.5 s的矩形脉冲表示“0”。同时在每帧数据的末尾有一个24 ?滋s长时间的低电平信号RESET以表示一帧数据的结束。

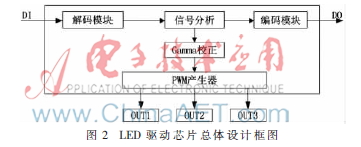

根据LED的驱动方式,本文设计的LED驱动芯片主要完成对输入信号分析、解码以及数据的转发,最后产生PWM波形控制R(红)、G(绿)、B(蓝)发光灰度的任务。总体设计框图如图2所示。电路的整体思路设计大致如下:芯片从DI口接收归零码格式的数据,解码模块完成输入数据的二进制码元的恢复并送往下一个模块进行数据锁存。Gamma 校正模块将信号分析模块输出的数据通过系数1.8的Gamma 视觉校正后输出11位宽度校正数据,最后由PWM产生器根据这11位校正数据产生相应的PWM输出波形,从而控制和点亮LED。PWM输出端口OUT0、OUT1、OUT2采用增强式PWM 控制,可实现2 048 级(11位)步进。这样的处理使得LED在低灰度显示时亮度的变化更柔和更平滑。

2 芯片各模块设计

2.1 解码与信号处理

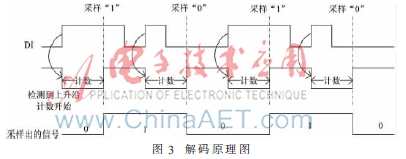

芯片输入的归零码数据中的“0”、“1”分别以不同占空比的矩形脉冲(归零码)表示。在这种码型中,数据都是以高电平开始,低电平结束,每个数据位的开始时刻都有一个上升沿。其解码原理如图3所示。

在每帧数据流的最后有不小于24 ?滋s的同步刷新信号以表示一帧归零码的结束。在具体的设计中可利用一个计数信号在24 s到来时将电路中的计数器和移位寄存器复位,以保证下一帧不会与上一帧数据发生错乱现象。同时还可利用该信号作为Gamma矫正和PWM数据刷新的触发信号以达到简化电路设计的目的。

数据输入端口接收完24位数据后即刻将后续数据转发至下一颗芯片中。每位数据都由上升沿开始,可以用数据的上升沿启动计数器。将计数器计数完24时的计数结果进行逻辑处理,可产生一个“0”→“1”跳变的高电平信号,用此高电平与输入数据相与,即可在转发端口处输出第25位及25以后的输入数据。

解码模块输出的数据为24位的串行数据,而Gamma 校正模块中的输入数据须为3个8位代表RGB信息的并行数据,故在设计Gamma校正模块前须将解码模块中解出的数据进行锁存且并行输出。

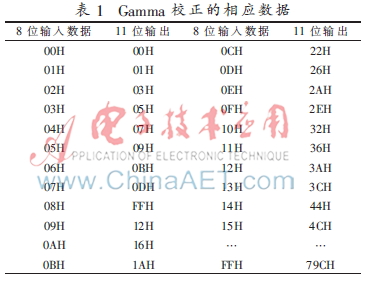

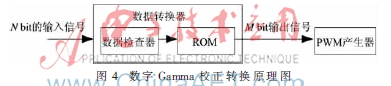

2.2 Gamma校正

本文中的驱动芯片接收的8位数据通过系数1.8的Gamma视觉校正达到2 048(11位)步进,这样的处理使得LED在低灰度显示时变化更柔和、更平滑。表1说明8位数据经过系数1.8的Gamma校正后的相应输出。本文采用数字查找表的方式设计Gamma校正,其原理框图如图4所示。数据检测器检测到数字信号后送往ROM查找表,然后在ROM查找表中查到与之相应的一个预先设定的Gamma值,最后将此Gamma值送往下一模块电路中。在这个方案中,ROM查找表的功能就是把N bit的输入信号根据ROM中寄存的值转化成相应的M bit输出信号。

本文的驱动芯片内部集成了一个ROM模块。由数据流经过解码和信号处理后得出的8位并行数据经过Gamma校正后输出相应的11位数据都被存储在这个ROM模块中,最后将ROM模块输出的11位数据送往PWM模块中。

2.3 PWM控制模块

本文中PWM控制模块电路的目的是要实现高亮度LED的亮度调制。LED驱动芯片RGB的输出端口采用PWM输出的方式,如果亮度值的编码为n bit,则LED就有2n个灰度等级。若LED的亮度值为D,则此LED在前D个状态时被点亮,在2n-D个状态下被熄灭,进而可以实现灰度级数值与PWM占空比的对应过程。

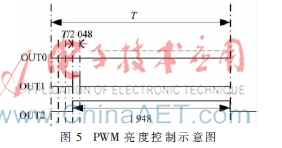

本文设计的驱动芯片的输出端口OUT0、OUT1、OUT2采用增强式PWM控制,接收的8位数据通过系数1.8的Gamma校正达到11位步进。因此,在本文中将PWM周期分成2 048(211)个等份,每个等份对应的时间周期为T/2 048,T代表PWM周期。在每个PWM周期开始时,LED全部点亮,然后根据亮度值决定此LED何时熄灭。亮度值为0时,表示LED在导通瞬间立即熄灭,亮度值最大时,则表示LED始终导通。但是由表1 中Gamma校正后的11位相应数据可知,在亮度值最大为FFH时,始终导通最大的周期为79CH,即为1 948,则本文可以设定最大的点亮周期为1 948。图5为PWM亮度控制示意图,图中 OUT0输出的是亮度值为0时LED熄灭的PWM波形; OUT1输出的是亮度值为1时的PWM波形,即占空比为1/1 948;OUT2输出的是亮度值为最大时LED最亮的PWM波形。

根据以上PWM控制原理的分析可知,PWM可分成三个部分:

(1)实现一个11位计数器计算PWM的周期。同时设计一个逻辑电路,运用逻辑关系可以使得计数器计数到1 947时输出置1的判决信号。

(2)设计逻辑电路分析出输入的亮度数据,并将比较的结果用于清零判定。该逻辑电路完成从ROM模块校正后输出的11位数据与PWM计数器产生的计数值从高位到低位形成异或的关系,从而得出一个比较值以判决这两组信号是否相同。若各位数相异或的结果都为0,则表示找到了11位数据在PWM模块中相应的等份值,否则其结果为1。这样可得到一个PWM输出清零的控制信号。

(3)PWM波形输出电路。当11位计数器由2 047计数到1 947时输出一个高电平信号。在此刻可以用高电平的上升沿触发一个D触发器,将D触发器的Q端输出置“1”,从而产生一个高电平脉冲。接下来把第二部分电路中产生的控制信号作为此高电平脉冲的清零信号。即异步计数器在1 947处产生一个高电平,同时若找到了ROM模块输出的11位数据在PWM模块中相应的值时将被触发置1的D触发器进行清零操作,这样就可以产生相应的PWM波形。

3 芯片总体功能仿真及版图设计

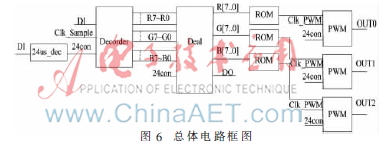

整个LED驱动芯片的总体电路框图如图6所示,其中DI为数据输入端口,DO为芯片级联端口,OUT0、OUT1和OUT2分别为RGB三基色的PWM波形输出端口。总体电路包括同步刷新信号检测电路24us_dec、解码电路decorder、信号处理电路deal、存储器ROM以及PWM产生器。根据输入数据的要求,本文解码模块的采样时钟clk_sample选取4 MHz(低速)或者8 MHz(高速), PWM产生器模块的计数时钟clk_PWM选取500 kHz。

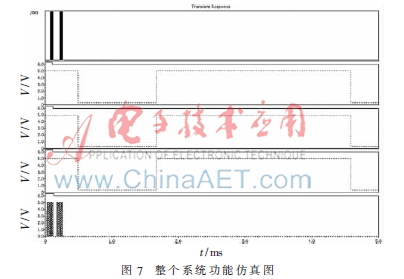

设计中将以上各个模块的电路进行连接,在Cadence软件中进行数模混合仿真[3],仿真结果如图7所示。

仿真的输入数据流为:第一帧数据为16个“1000 1000 1000 1000 1000 1000 1000 1110”,第二帧数据为16个“1000 1110 1000 1110 1000 1110 1000 1110”,第一帧与第二帧之间相隔200 ?滋s的低电平。图中下方为DI输入的两帧数据,上方DO为自动转发出的两帧数据。由于文中PWM模块的计数时钟clk_PWM选取500 kHz,则一个PWM的周期为4.096 ms。相隔200 s的刷新信号不足以产生一个完整PWM波形,故第一帧数据无法输出PWM波形,图中的RGB所表示的PWM波形是由第二帧数据产生的。在实际应用中,将本文设计的LED驱动芯片RGB的PWM输出端与高亮度LED的RGB 3个脚分别相接,即可控制高亮度LED色彩和亮度。

后端设计在Cadence软件中采用CSMC05的工艺完成。为了使LED驱动芯片版图在面积和性能上实现最优化,本文采用全手工布局布线的方式完成版图设计。根据具体的逻辑,将相应的标准单元从单元库中调出,排列成行,根据相邻两行的需要和布线的规则,决定布线通道,进行布线和I/O端口的连接,完成整个版图的设计[3]。版图包括8个输入输出保护单元和压焊块,近200个逻辑门共3 000多个MOS器件,版图面积为898.4 m×972.05 m。本文的驱动芯片完全通过dracula的DRC和LVS验证,并在2012年2月送往华润上华进行加工制作。目前芯片已加工制作完毕,测试结果正常,完成了预定的功能。

4 结束语

本文提出了一个完整的三通道高亮度LED驱动芯片的ASIC设计方案。设计出的芯片采用单极性归零码的方式收发数据,且采用自动整形转发技术,使得该芯片的级联个数不受信号传送限制,仅受限于刷屏速度的要求。同时,芯片的输出端采用增强式PWM控制输出,所接收的归零码经解码后的8位数据通过系数1.8的Gamma 校正可达到2 048级(11位)步进,使得在低灰度显示时变化更柔和更平滑。后端采用CSMC05工艺,综合考虑电路性能、成本等因素,利用全定制的方式完成整体芯片版图的设计。本文设计的LED驱动芯片能适用于装饰灯串、广告模组、信息屏等应用场合,有较好的商业价值。

参考文献

[1] 杨恒.LED照明驱动电路设计与实例精选[M].北京:中国电力出版社,2008.

[2] RABAEY J M,CHANDRAKASAN A,NIKOLIC B.数字集成电路:电路、系统与设计:a design perspective[M].北京:电子工业出版社,2010.

[3] BRUNVAND E.数字VLSI芯片设计——使用Cadence和Synopsys CAD工具[M].北京:电子工业出版社,2009.

[4] 小林芳直.数字逻辑电路的ASIC设计[M].北京:科学出版社,2004.

[5] 猪饲国夫,本多中二.数字系统设计[M].北京:科学出版社,2004.

[6] 孙学军.通信原理[M].北京:电子工业出版社,2007.

[7] 李桂宏,谢世健.集成电路设计宝典[M].北京:电子工业出版社,2006.

[8] 曾庆贵.集成电路版图设计[M].北京:机械工业出版社,2008.