摘 要: 介绍了嵌入式处理器在使用基于SPI引导方式时,如何检查DDR内存,以提高系统的可靠性。对系统的引导过程,包括片内ROM运行、片内RAM运行、DDR内存运行,进行了详细的介绍。对各阶段引导程序数据格式的处理进行细致的分析,并对生产实用化进行了实例验证。

0 引言

随着全球网络进一步扩展到新终端设备和以前未连接的行业中,网络安全对消费者、企业和其他机构变得越来越重要。人们越来越需要性能安全、价格便宜的装置设备。为了降低成本,往往需要简化电路设计。例如,采用SPI方式引导硬件,使用SPI Flash作为存储媒介,减少总线的布线,是简化硬件电路的较好的方法[1]。但采用SPI方式引导硬件,需要将程序引导到DDR内存中,同时又需要对DDR内存进行检查,这就出现了矛盾[2]。

1 基于SPI的硬件引导

本文以一个实例,对嵌入式处理器基于SPI引导硬件时如何进行RAM检查进行详细的介绍。图1是嵌入式处理器使用SPI引导的硬件框图。在图1中,硬件引导程序和系统程序放在SPI Flash中,在上电引导后,系统程序会被搬移到DDR空间,在DDR空间运行起来。

现在以U-Boot硬件引导程序为例,介绍以SPI引导模式引导系统硬件的情况。U-Boot是德国DENX小组的开发用于多种嵌入式CPU的Bootloader程序,可以支持多种嵌入操作系统和多种处理器[3]。

编译的U-Boot程序,往往是运行在NOR Flash或DDR中的。但在基于SPI引导时,需要先从SPI Flash往片内RAM里运行一段程序,将DDR内存检查一遍,然后再将U-Boot引导到DDR内存中去运行,如图2所示。

2 SPI引导采用的数据格式

在TI公司的DSP及ARM处理器,飞思卡尔公司POWERPC及ARM处理器,都支持基于SPI的引导模式。在这些处理器的片内ROM都包含基本的SPI引导驱动程序。本文以飞思卡尔公司的QorIQ P1010处理器为例介绍其引导过程。P1010片内的SPI驱动程序能够把SPI接口Flash中的程序拷贝到DDR内存或片内RAM中。不过,在拷贝之前,需要先对DDR控制器或片内RAM进行配置。这就需要定义一个特定的数据结构,完成引导程序所需要的环境配置。对于不同的处理器,生产厂家定义的引导数据结构是不同的。

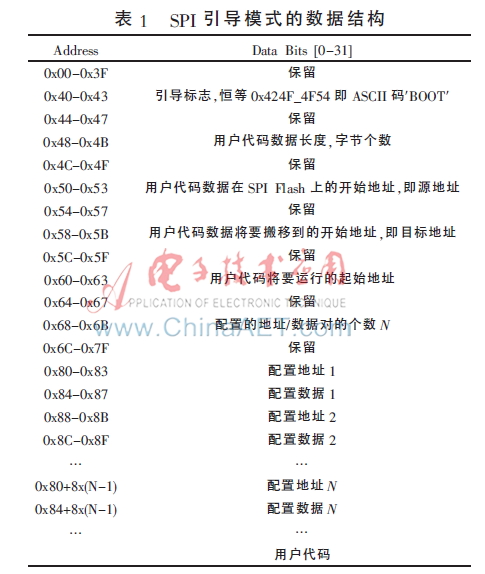

在P1010处理器完成复位序列后,通过选择使用处理器片内ROM的SPI引导配置程序,而后处理器内核开始运行该片内ROM程序,配置SPI控制器,并与外部的SPI Flash通信,将程序拷贝出来并跳到指定的位置运行[4]。SPI引导采用的数据格式如表1所示。

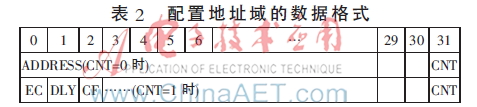

在表1中,配置字(Control Words)由配置32 bit地址/数据对组成,主要用在配置就地访问窗口(LAW)和目标内存控制器的寄存器。配置地址域有两种模式,当最低位为0时,配置地址域高30 bit代表的是地址,此时配置数据写入此地址。当最低位为1时,配置地址域高30 bit代表的是指令,此时配置数据写入此地址。这样的结构让用户可以方便地配置4 B对齐的内存,完成控制指令操作,或定义程序配置阶段的结束[5]。配置地址域的数据格式如表2所示。

在表2中,当CNT(最低位)=0时,则高30 bit用作要写入数据的地址,配置数据包含要写入的数据。

当CNT=1时,则高30 bit用作控制指令。

当EC=1时,代表配置阶段结束指令。

当DLY=1时,代表延时一定时间指令。

当CF=1时,代表更改SPI频率的指令。

CNT表示地址模式与指令模式的切换。

当处理器内核开始拷贝程序时,先判断0X40位置的标志是否正确,如果正确,先根据配置的地址/数据对的个数N来配置一些外围寄存器,然后从0X50处指示的Flash地址搬移用户代码数据到0X58指示的地址。搬移完成后,从0X60指示的地址开始运行。将片内运行的这一段程序叫TPL程序。

3 片内RAM运行的TPL程序

P1010包含256 KB的L2CACHE,也可以当片内RAM使用。要检查DDR内存,要先在片内RAM里运行一小段TPL程序。这一段程序是对基于DDR引导程序U-Boot的一个裁剪,主要完成内核的配置,初始化串口终端,初始化DDR内存控制器,然后检查DDR内存[6]。在这里不需要设置U-Boot的环境变量,不需要配置以太网等其他的外围器件。编译后的TPL目标文件为uboot-tpl.bin。

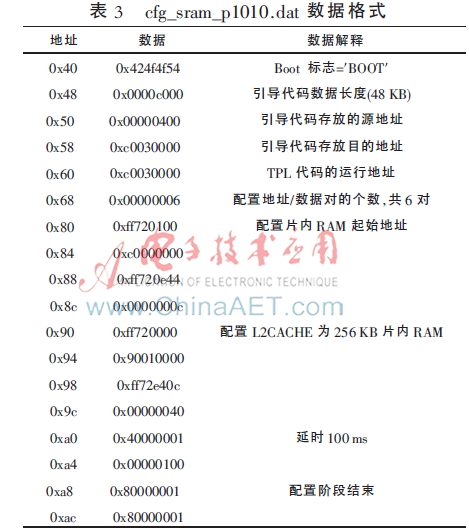

TPL程序的编译按RAM引导的方式处理。程序的开始地址设为:0xc0030000~0xc0038800。现在需要对编译后的uboot-tpl.bin进行格式处理,在其前面加上SPI引导的可以识别的数据表头,如表3所示。

表3是按照表1(SPI引导模式的数据结构)和表2(配置地址域的数据格式)完成的一个SPI引导配置实例。在这个实例中,将L2CACHE设为片内RAM,开始地址设为0xc0000000。这一部分空间在处理器内核引导时已经通过TLB映射,可以直接使用。

对TPL进行数据格式化存放,要用到一个工具,即boot_format,它可以将基于HEX的文件和基于BIN格式的文件合并到一起。这是一个飞思卡尔BSP里带的数据格式化工具。采用以下命令:

./boot_format cfg_sram_p1010.dat uboot-tpl.bin-spi uboot_tpl_spi.bin

合并后的文件为uboot_tpl_spi.bin。

在cfg_sram_p1010.dat文件里,TPL程序存放在SPI Flash的0X400开始的地址。处理器先对片内RAM进行配置初始化,然后将TPL程序从0X400引导到0xc0030000开始的地址,并从0xc0030000开始运行。这时,处理器对DDR控制器进行配置,并对DDR空间进行自检。

4 DDR的自检及U-BOOT的运行

DDR RAM的自检可以采用写入特定数据(例如0x55,0xAA),然后回读比较来检查的方式;也可以通过检查行列地址数据线来检查。相关文档很多,这里就不介绍了。

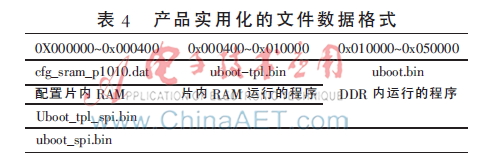

当检查完DDR内存后,就可以引导并运行U-Boot程序了。U-Boot程序按RAM引导的方式编译。程序起始地址设为0X11000000。编译后的文件为uboot.bin。但在实际中需要将两个单独的BIN文件合并成一个文件,以方便生产和产品实用化。当uboot.bin与uboot_tpl_spi.bin合为的一个文件uboot_spi.bin时,uboot_tpl_spi.bin放在前面,uboot.bin程序放在后面,如表4所示。

在表4中,处理器在运行TPL时,将U-Boot从SPI Flash的0X10000地址引导到DDR3的0X11000000开始的地址(代码数据总长度0x40000),而后跳运行入口地址(0X1103f000),运行U-Boot程序。这时,整个硬件系统引导起来了。操作系统可以通过U-Boot运行起来。

5 结论

嵌入式处理器在使用SPI引导硬件时,先通过片内RAM运行一段程序,对DDR内存进行自检,而后再将U-Boot程序及环境变量引导到DDR空间[7],把硬件系统引导起来。通过实例化的应用,证明这在高性价比的嵌入式应用中是一个不错的选择,不仅能提高系统的可靠性,而且简单易行。

参考文献

[1] 张伟栋,赵红.基于PowerPC8640处理器的通用处理模块设计[J].微型机与应用,2015,34(6):32-34.

[2] 李相国,杨树元.基于PowerPC处理器SMP系统的U-Boot移植[J].微计算机应用,2008,29(9):95-99.

[3] 王齐.Linux PowerPC详解:核心篇[M].北京:机械工业出版社,2007.

[4] 李宗海,陈蜀宇,李海伟.嵌入式Linux系统在ARM平台上的构建[J].计算机系统应用,2010,19(10):153-157.

[5] Freescale Semiconductor, Inc. Booting from On-Chip ROM (eSDHC or eSPI) [EB/OL]. (2012-6-1)[2014-4-18].http://cache.freescale.com/files/32bit/doc/ app_note/AN3659.pdf.

[6] 邓国荣,刘厚钦.基于NOR Flash的OMAPL138双核系统自举引导启动实现[J].电子技术应用,2014,40(2):19-26.

[7] 邹洋,李琳皓,梁峰.Nucleus操作系统在ARM11上的移植研究与实现[J].电子技术应用,2014,40(9):10-13.