新型CEVA-X4 DSP首度把深层神经网络引入嵌入式系统

2016-03-24

作者:杨庆广

来源:电子技术应用

世界上每三部手机中就有一部有CEVA基带DSP,CEVA已占据DSP IP主要市场份额,超过任何其它DSP IP供应商三倍以上。大家耳熟能详的三星、英特尔、中兴、联发科、新岸线、展讯等公司都是CEVA的客户。近期CEVA推出新型CEVA-X DSP 架构框架,可以胜任日益复杂的基带设计,适用于广泛的应用场景,包括LTE-Advanced 物理层控制、机器通信(MTC)和无线连接技术等。

CEVA市场营销及企业发展副总裁Eran Briman

“特别值得注意的是,CEVA-X4——基于新型CEVA-X DSP架构的首款内核,由于具有强大的性能,可以在嵌入式系统中顺利运行CDNN(深层神经网络)。CDNN使得嵌入式系统执行深层学习任务的速度比基于GPU的领先系统提高3倍,同时消耗的功率减少30倍,所需存储带宽减少15倍。” CEVA市场营销及企业发展副总裁Eran Briman表示。

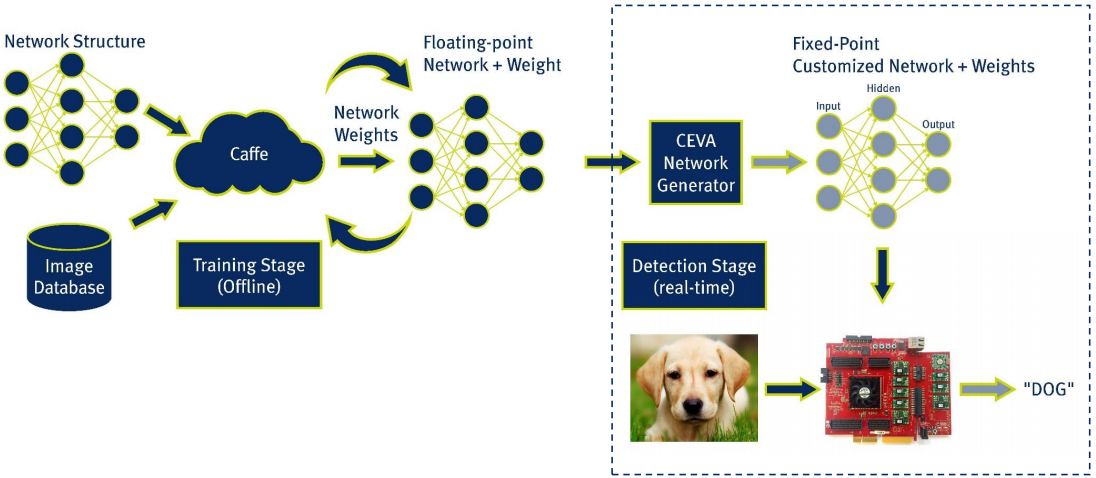

CEVA深层神经网络模型

Eran Briman进一步解释说:“首先,通用的神经网络结构,在离线状态下在大型服务器上做训练,形成数据库,这大约需要一周或几周时间,最终输出一个适用于某类应用专门优化的神经网络,这个神经网络具有浮点权重,最终决定运转的过程。接着,将经过训练的浮点数据组成的神经网络嵌入终端时需要做处理,因为这些浮点数之前运行在大型服务器上,非常复杂。让它运转在低功耗的终端平台上,有几个步骤。先通过CEVA开发的神经网络转换工具,把复杂的浮点数网络转化成定点数表达的神经网络,然后把神经网络加载到XM4的运转平台上,这样,这个嵌入式设备就有非常强大的处理能力。”

CEVA-X4架构图

新型CEVA-X使用可扩展的VLIW/SIMD架构、高达128位SIMD、可变流水线长度和支持定点运算和浮点运算。与前一代CEVA-X相比,新型CEVA-X可以提供2倍以上的DSP性能,而功耗却低50%。这种架构还包括专用32位零延迟指令集架构(Instruction Set Architecture, ISA)、32位硬件除法和乘法、动态分支预测和超快上下文转接,以提供现代基带设计要求的高效控制处理。

CEVA-X4是基于新型CEVA-X DSP架构的首款内核,瞄准 2G/3G/4G/5G基带中multi-RAT多载波P物理层控制处理中最复杂的工作负荷。

最新的CEVA-X4基带应用处理器将为下一代调制解调器提供更加优异的性能。

下一代调制解调器架构

CEVA-X4将解决新一代调制解调器设计中面临的三个关键挑战。

首先是高效控制处理:对于多载波聚合来说,L1 PHY控制处理显着增加。例如,并行处理高达5个载波分量和在多个载波上顺序处理多个PHY控制任务,需要新一代Rel-13 LTE Advanced Pro调制解调器。

其次是强大的DSP处理:需要显着提高DSP的性能以支持繁重的LTE工作负荷,包括逐个信道测量、校正和解码,以及其他RAT标准。

最后是先进的系统控制:为了以较低的延时限制方式处理系统中的多个加速器、DSP和共处理器,需要开展复杂的系统调度和数据通信管理。