冯建文,王春

(杭州电子科技大学 计算机应用所,浙江 杭州 310018)

摘要:介绍了FPGA远程实验系统的组成、工作原理以及远程配置,着重介绍FPGA远程实验系统的远程配置的原理及具体实现,即在ARM微控制器的主导下,通过以太网实现FPGA配置数据的传输和下载,然后由ARM作为时序控制器,通过FPGA的从串(slave serial)配置方式,完成FPGA的远程配置。在FPGA配置的同时,通过研究配置管脚输出的波形,来验证FPGA从串配置模式下的配置原理。

关键词:FPGA;远程实验系统;远程配置;ARM

0引言

近年来,使用可编程器件 FPGA/CPLD 和 VHDL 进行硬件设计发展快速,可编程逻辑器件逐渐取代了传统通用的中、小规模集成电路而得到广泛的应用,并且随着系统的复杂程度越来越高,借助在电子系统的开发过程中具有重要作用的EDA(Electronic Design Automation)软件,使得FPGA 成为数字逻辑电路设计、计算机组成原理、嵌入式系统等课程实验教学的首选方式[1]。同时随着嵌入式技术以及网络技术的发展,远程控制也变得越来越容易实现,把远程控制技术引入到FPGA实验系统中来,利用FPGA可重复编程的特点,实现FPGA实验操作远程执行,从而实现实验设备的远程共享和实验设备的最大利用。

1FPGA工作原理及配置

现场可编程门阵列(Field Programmable Gate Array,FPGA)是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点[2]。以硬件描述语言(Verilog或VHDL)所完成的电路设计,可以经过简单的综合与布局,快速烧录至FPGA上进行测试,是现代 IC设计验证的技术主流。

FPGA利用小型查找表(16×1 RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。在FPGA正常工作时,配置数据存储在SRAM单元中,这个SRAM单元也被称为配置存储器(Configuration RAM)。由于SRAM是易失性的存储器,因此FPGA在上电之后,外部电路需要将配置数据重新载入到片内的配置RAM中[3]。FPGA的配置过程如下:外部电路将配置数据载入片内配置RAM中;片内配置RAM中的配置数据用于控制FPGA内部可编程的内部逻辑、内部寄存器和I/O寄存器初始化、I/O驱动器使能等。配置完成后,FPGA进入用户模式。在掉电后,FPGA又恢复成白片,内部逻辑关系消失。

FPGA一般有4种配置模式:从串模式(Slave Serial)、主串模式(Master Serial)、从并模式(Slave Parallel/SelectMap)以及边界扫描模式(Boundary Scan)。配置模式的选择一般由FPGA芯片上配置模式选择引脚的输入电平决定[4]。

从串配置模式是指在进行配置时,由外部控制器主导同步时钟输入,将配置数据一位一位地加载进FPGA;主从配置模式则是在FPGA内部同步时钟的作用下,将配置数据从外部存储器按位串行加载到FPGA中;从并模式则是将配置数据多位数据一起并行输入;而边界扫描模式即JTAG配置模式,JTAG模式在开发调试阶段使用。

2基于ARM的远程实验系统

基于ARM的远程实验系统主要功能是实现远程FPGA的实验操作。用户通过该系统,能够在PC端登录该实验系统,进行预约FPGA实验,同时能够发送FPGA控制命令,并且能够得到实验结果信息。系统结构如图1所示,主要分为3个模块:PC客户端、服务器端和ARMFPGA模块。PC客户端为用户提供远程实验操作接口,服务器端则主要负责数据或命令的发送和接收,而ARMFPGA模块则是进行控制和执行客户端发来的命令,并向服务器返回实验结果。

2.1PC客户端

客户端的主要作用是提供用户操作接口,为用户提供远程操作ARM控制器的界面,方便用户控制FPGA的配置及相关的FPGA实验操作。客户端的设计主要采用C/C++编程,采用Socket编程模式进行配置数据的发送和配置结果数据的返回。

2.2服务器端

服务器是基于FPGA实验平台的远程实验系统的核心,负责控制实验系统的运行。它负责FPGA实验平台的调度管理,给实验用户(PC客户端)分配空闲的实验平台。并且需要能连接上百个ARM客户端和PC客户端,作为两种客户端之间的信息中转站。同时,服务器还负责管理数据库,及时进行学生信息、FPGA平台信息、预约记录和实验记录等信息的记录和更新。

2.3ARM客户端

ARM客户端作为系统整体结构中的重要组成部分,是与FPGA实验平台进行数据交互的唯一接口,它主要实现如下功能:

(1)连接服务器,接收PC客户端发来的指令信息,还需接收存储FPGA配置执行文件。

(2)解析指令,调用程序完成指令。

(3)实现FPGA动态配置,把配置文件加载到FPGA运行。

(4)连接PC客户端,实时将FPGA相关引脚的信息发送到PC客户端。

(5)实现对FPGA实验平台上开关、按键的远程控制操作。

3FPGA远程配置的实现

在本次实验中,选用ARM9开发板+FPGA实验板来完成FPGA远程配置的具体实现。其中ARM控制器采用以ARM9为处理器的单片机开发板。ARM9开发板支持网络接口连接,并且成功地移植了Linux 2.6.30内核操作系统以及相应的文件系统,为Socket网络编程和ARM客户端的软件实现与执行提供了良好的Linux环境。FPGA则使用为计算机组成原理所设计的FPGA实验板卡,该实验板卡所用的FPGA芯片为Xilinx生产的Spartan-6系列芯片,并将其专用的配置接口引出,方便后续的实验操作。

3.1配置文件

本设计所用的FPGA的配置数据格式为.bin格式,是由Xilinx的FPGA设计工具ISE软件产生的FPGA配置数据的一种格式,也是进行Spartan-6系列芯片进行从串配置的配置数据格式。在PC客户端可通过Socket编程配置引脚

将文件由网络传送至ARM控制器客户端。

3.2配置电路

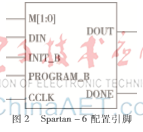

Spartan-6配置引脚如图2所示,各个引脚的功能如表1所示。表1FPGA配置引脚说明引脚名类型说明M[1:0]输入模式选择引脚,决定FPGA的配置模式CCLK输入/输出除JTAG配置模式外其他配置模式的同步时钟源DIN输入串行配置数据输入引脚,同步于时钟的上升沿DOUT输出用于菊花链配置器件后面的器件配置数据的串行输入DONE输出高电平表示配置完成,低电平表示配置失败INIT_B输入/输出在配置模式选择完成前,拉低该引脚电平表示延迟配置;配置模式选择完成后,该引脚的电平输出表示配置有无发生CRC校验错误:

0=CRC error

1=No CRC errorPROGRAM_B输入低电平输入使芯片复位

3.3配置流程

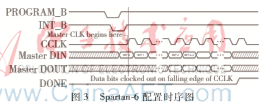

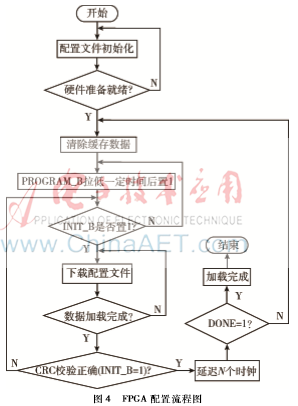

Spartan-6芯片的配置时序如图3所示,先给PROGRAM_B引脚一个低电平信号,然后再恢复高电平,检测INIT_B引脚电平信号,如果其电平信号也随着PROGRAM_B而变化,则表明FPGA内部配置已经完成初始化,可以进行FPGA配置了。接下来在ARM输入到FPGA的DCLK引脚的信号的同步下,按位加载配置数据,直到加载完配置数据。当检测到DONE引脚信号变为高电平时,表明FPGA已经完成配置,进入到工作状态了。其配置程序的流程图如图4所示。

4实验结果分析

实验时,将FPGA的配置引脚DIN、CCLK、INIT_B、DONE、PROGRAM_B连接到ARM开发板的I/O引脚上,同时注意ARM开发板和FPGA实验板卡要共地,将ARM开发板接上网线,供电并启动后,通过PC客户端进行配置文件的传输和加载,当配置完成后返回客户端“config done!”则表示配置完成。实验结果演示如图5所示。

为了得到配置过程中DIN引脚和CCLK引脚的数据,在程序中进行了配置数据输出,并用示波器捕捉到这两个引脚的输出波形,如图6所示。由图可以看出,在一个配置循环中,ARM控制器是按字节进行位传输的,每个字节8位数据,在每输入一个时钟过程中,输入一位配置数据,直至加载完所有配置数据,完成FPGA的配置。

5结论

本设计中采用两个独立模块的连接来实现总体功能,而且ARM控制器的一些操作命令是通过串口进行命令传输实现的。在接下来的FPGA远程实验系统中,将完全通过单网线进行ARM所有操作命令的实现,并且不仅能完成FPGA的远程配置,还能完成FPGA的远程实验——远端实、近端虚的远程FPGA实验,即在客户端电脑上完成界面上开关、按键等操作,这些操作命令通过网线传递到ARM端,控制FPGA相关引脚的输入高低电平,并返回相关引脚的输出电平,在客户端电脑上通过LED或数码管来显示该引脚电平的高低。

参考文献

[1] 丁伟, 肖铁军. 基于FPGA的通用实验平台的设计与实现[J]. 无线通信技术, 2013, 22(4):38-39.

[2] 刘笑嫘, 何广平. FPGA芯片的配置与下载[J]. 科技信息, 2011(15):109-109.

[3] 高闯, 吴利华, 芳罗,等. 一种用于FPGA的可配置存储器设计[J]. 固体电子学研究与进展, 2016,36(1):67-67.

[4] 陈曦, 沈佐峰. 一种可靠的FPGA动态配置方法及实现[J]. 通信技术, 2012, 45(3):105-107.