FPGA IO口时序约束是怎么一回事?

2017-01-13

关键词:

FPGA时序

补充:

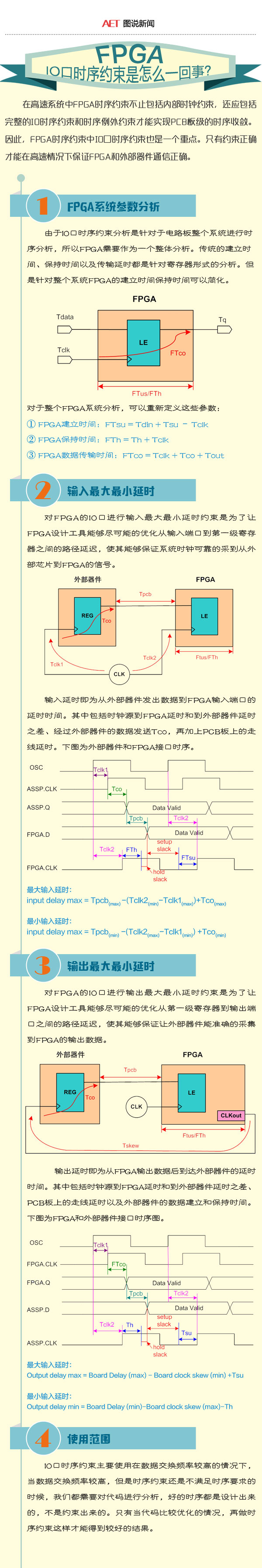

一、参数定义:

(1) Tdin为从FPGA的IO口到FPGA内部寄存器输入端的延时;

(2) Tclk为从FPGA的IO口到FPGA内部寄存器时钟端的延时;

(3) Tus/Th为FPGA内部寄存器的建立时间和保持时间;

(4) Tco为FPGA内部寄存器传输时间;

(5) Tout为从FPGA寄存器输出到IO口输出的延时;

(6)Tpcb为PCB走向延迟。

二、进行输入最大最小延时的计算,我们需要估算4个值:

(1) 外部器件输出数据通过PCB板到达FPGA端口的最大值和最小值Tpcb,PCB延时经验值为600mil/ns,1mm = 39.37mil;

(2) 外部器件接收到时钟信号后输出数据延时的最大值和最小值Tco;

(3) 时钟源到达外部器件的最大、最小时钟偏斜Tclk1;

(4) 时钟源到达FPGA的最大、最小时钟偏斜Tclk2。

三、进行输出最大最小延时的计算,我们需要估算4个值:

(1) FPGA输出数据通过PCB板到达外部器件输入端口的最大值和最小值Tpcb,PCB延时经验值为600mil/ns,1mm = 39.37mil;

(2) 时钟源到达外部器件的最大、最小时钟偏斜Tclk2;

(3) 时钟源到达FPGA的最大、最小时钟偏斜Tclk1;

(4) 外部器件的建立时间Tsu和保持时间Th。

本站内容除特别声明的原创文章之外,转载内容只为传递更多信息,并不代表本网站赞同其观点。转载的所有的文章、图片、音/视频文件等资料的版权归版权所有权人所有。本站采用的非本站原创文章及图片等内容无法一一联系确认版权者。如涉及作品内容、版权和其它问题,请及时通过电子邮件或电话通知我们,以便迅速采取适当措施,避免给双方造成不必要的经济损失。联系电话:010-82306118;邮箱:aet@chinaaet.com。