李春雨

(浙江机电职业技术学院,浙江 杭州 310053)

摘要:在基于mTCA规范的媒体网关系统中,两块主控制板要求热备份,当一块主控板故障时,另一块主控板需自动升主,替代故障板。对现有的主备倒换方案进行了分析,并改进了现有方案,该方案通过高低温老化测试,工作可靠。

关键词:媒体网关;CPLD;主备倒换;热交换;主控板;背板;

中图分类号:TN79文献标识码:ADOI: 10.19358/j.issn.1674-7720.2016.24.012

引用格式:李春雨. 媒体网关系统中的主备倒换设计改进方案[J].微型机与应用,2016,35(24):40-41,49.

0引言

主控板是媒体网关中的大脑,管理和维护系统中的其他单板,与上位机通信,传递信令信息,要求全年无故障工作,主备倒换技术是提高通信设备可靠性的重要解决方案之一[1],因此媒体网关中的主控板需要热备份,当一块板故障后,另一块备用板立刻升主,平滑切换。本文着重研究小型媒体网关中主控板的主备倒换。

1主控板的硬件设计

媒体网关中主控板管理其他业务板,加载其他业务板,分发时钟,监控风扇板和电源板的状态。主控板的框图如图1所示。

处理器采用RMI公司的XLS408,通过可编程逻辑器件接三个外设:(1)FPGA:主要实现32路智能管理总线,管理、监控、加载业务板。(2)SA8000:该芯片是时钟芯片,产生高精度的38.88 MHz时钟。(3)SA586:该芯片是E1信号收发芯片。

鉴于主控板的重要地位,它要求全年无故障工作,需支持主备板热备份。所谓热备份,即媒体网关机框上电时,有两块电路结构完全相同的主控板,根据所在的槽位是奇槽位还是偶槽位区分出主板和备板,完全启动之后,业务都运行在主板上,备板不参与业务控制,但主板会将自己保存的信息同步到备板上,这个过程称为热备份[2]。

2现有的主备倒换方案

方案1:基于FPGA的主备倒换方案[3],该方案实现框图如图2所示。

图2基于FPGA的主备倒换方案该方案基于FPGA实现主备倒换逻辑,图2所示6个信号通过背板实现本板和备用主控板的传递,在CPU控制下实现倒换,其优点是稳定性好,但缺点是FPGA基于RAM结构,每次上电FPGA代码都要从一个外部存储设备加载到内部的RAM中[4],系统上电时由控制器读出配置数据再传送给FPGA进行配置[5]。这个配置过程和配置数据大小与配置时的加载时钟关系很大,一般需要几秒钟甚至几分钟,延长了倒换时间。

方案2:基于CPLD的主备倒换方案[6],该方案实现如图3所示。

该方案用CPLD代替FPGA,可以解决FPGA加载慢的问题,CPLD内部代码存储采用Flash机制,不需要从外部加载,启动时间为1 ms,因此使用CPLD倒换速度会大大提高。

但是在实际异常测试和振动试验中发现,该方案存在双主的故障,即两块主控板同时作为有效的主用板工作,造成输出信号冲突。经分析,由于媒体网关上板卡多,信号多,高密度互连背板通常使用专用的连接器,如华为的UAP6600上主控板使用的背板连接器中用的FCI公司的AIRMAX连接器,而且要用图4所示的7组连接器[7],在产品的振动试验中发现经常出现双主现象。因此上述基于CPLD的主备倒换方案也存在问题。

3改进的主备倒换方案

3.1硬件改进措施

基于异常测试和可靠性测试结果,下面分析方案2出现双主的原因。

媒体网关上有多块板卡插在背板上,主控板和背板的连接器采用图4所示方案,7个54管脚的AIRMAX连接器压接到背板上,图5是对板主备指示信号(ACT_VS信号)在连接器上的位置。

由于压接工艺的关系,存在连接器不平整、AIRMAX连接器没有短针、单板拔出时插稳信号还没断开但是ACT_VS脱离等现象;单板插入时,也会出现插稳信号已接触到而ACT_VS还没有连接, 从而ACT_VS检测不到,导致本板认为对板已经降备,因此本板升主,出现双主现象。

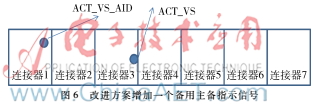

改进方案是:增加一个辅助对板主备指示信号,靠近边缘的连接器,辅助对板主备指示信号靠近插稳信号,如图6所示。

3.2逻辑代码改进措施

机框上电后,两块主用板同时为主,但是偶槽位主控板在18个CPLD工作时钟后就退出主用状态,奇槽位主控板一直为主。CPLD内代码用Verilog[8]语言编程实现,程序流程图如图7所示。

3.3改进方案的倒换时间计算

机框上电后,18个CPLD时钟周期后,偶槽位8号主控板退出主用,31个时钟周期后,奇槽位7号主控板退出主用,所以正常情况都是7号槽位的单板处于主用状态。工作后,从图7可以看出,如果8号槽位单板4个时钟周期检测不到对板送来的ACT_VS和ACT_VS_AID信号,则本板升主,如CPLD工作时钟为15 ns,则倒换时间为4×CPLD CLK=4×15 ns=60 ns。

4结论

媒体网关上背板和主控板连接信号很多,各类信号超过350个,必须采用适合高密度背板的连接器,而连接器由于压接工艺的问题,存在主用板接收不到ACT_VS信号的情形,采用上述解决方案,进行多次异常测试和振动测试,未出现问题。

参考文献

[1] 李洁,黄婷熙,潘涛涛. 高可靠性通信设备主备倒换软件实现方法[J]. 电视技术,2013,37(11):170 172.

[2] 张玉峰,孙知信. 基于热备份的主备倒换在高端路由器中的应用[J]. 计算机技术与发展,2010,20(3):172 175,179.

[3] 谭宇,姚亚峰,陈登,等. 基于FPGA主备倒换的电路设计与实现[J]. 电视技术,2014,38(11):82 85,102.

[4] 李春雨,张丽霞. 利用CPLD提高FPGA加载速度[J]. 电子器件,2013,36(4):550 553.

[5] 李春雨.基于CPLD的FPGA从并快速加载方案[J].中兴通讯技术,2014,20(4):57 59.

[6] 施世华,高西全,靳松杰,等.高可靠性通信设备的主备倒换设计[J].电子科技,2007(7):47 50.

[7] Fleck Research.AirMax VS Connector System[EB/OL].(200909xx)[2016 07 19]http://www.fci.com/.

[8] 王静霞.FPGA/CPLD应用技术(Verilog语言版)[M].北京:电子工业出版社,2011.