在VoIP媒体网关设备中,语音压缩编码是其关键技术之一。在ITU-T发布的应用于VoIP的语音压缩编解码标准中,G.729是应用较为广泛的一种。G.729采用“共轭结构代数码本激励线性预测编码”(CS-ACELP)算法,算法帧长为lO ms,编码后速率为8 Kb/s。G.729有两个附件:附件A给出一种低复杂度的算法,可应用于多媒体同步语音和数据;附件B在标准算法的基础上增加了静音检测压缩算法以降低平均传输率,包括静音检测(VAD)和舒适噪音产生(CNG)。文献对G.729语音压缩编码算法的具体原理中有详尽的描述,本文的论述重点在算法的汇语言优化、声码器的DSP硬件接口设计,以及其在媒体网关中的应用。

1 G.729ab编解码核心算法优化

本文选择TI公司的TMS320C6203芯片为核心,实现G.729ab声码器设计。TMS320C62xx系列DSP的集成开发环境Code Composer Studio(简称CCS)支持标准C语言和汇编混合编程的方式编程,为了提高编解码算法的效率,本文对ITU_T的标准G.729ab的C语言原码进行汇编指令优化设计。同时,对于上层编解码器控制函数,采用C语言开发,以提高声码器的可维护性。

C62xx采用6级流水线结构,提供了A,B两组(共32个)通用寄存器,8个功能单元(.L1,.L2,.S1,.S2,.M1,.M2,.D1和.D2),最多同时可以有8条指令处在不同的执行阶段并行。流水线结构是DSP实现高速运算的重要技术。由于不同指令的指令周期不同,需要在多周期指令后插入足够的NOP(空操作)指令,以避免流水线冲突。

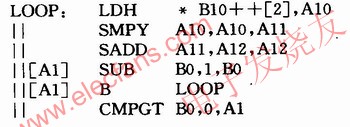

在G.729ab的标准C代码中,有大量的循环体。循环控制的关键跳转指令B,需要等待5个指令周期,大量的NOP操作将降低代码的效率。为了提高循环效率,可以合理安排指令顺序,在一个汇编循环体内完成多个C循环的运算的流水线操作。用汇编指令实现如下简单的for循环求信号能量的程序段为例:

上述示例可使用如下汇编程序段实现:

如上优化后,循环体LOOP仅为一个周期,在这一个周期中有6条并行运行的指令。其中,内存读取指令LDFI需4个周期,故乘法指令SMPY是将向前追溯4个循环周期的内存读取结果相乘。同理,SMPY指令需2个周期,故SADD指令是将2个循环周期之前的相乘结果相加。B0和A1配合用于循环控制,在等待跳转指令B有效的5个延时周期内,依次进行随后的后一循环的取数,前第3个循环的相乘,前一个循环的求和、循环控制和跳转指令,依次类推。上述优化实现了最优循环效率。

本设计优化后核心编解码算法代码完全符合ITUT G.729ab标准,并通过了ITU-T的所有测试矢量。使用300 MHz主频的TMS320C6203实现声码器,单片可支持31路G.729ab算法。

2 声码器的DSP硬件接口设计

在媒体网关中,声码器的功能是实现PSTN的E1语音信号和数据网分组语音压缩信号之间的编解码转化。利用TMS320C6203片内固化设置的McBSP接口(多通道缓存串行接口)与HPI接口(主处理器接口),可以实现DSP与E1总线、以及数据网上层处理器的连接。结构示意图如图1所示。

TM320C6203通过内置McBSP与EDMA(Enhanced Directory Memory Access,增强型直接内存访问)控制器配合,可实现与E1标准接口的链接。设置McBSP的接收/发送控制寄存器(R/XCR),使串口按照标准E1数据格式进行数据收发;设置串口管脚控制寄存器(PCR),控制串口采用外部E1总线的时钟和帧同步信号;设置串口控制寄存器(SPCR),控制串口的R/XINT(收/发中断)由EDMA响应。

TMS320C6203支持16个EDMA通道,其12~15通道可用于响应串口收、发中断。以串口接收数据为例:本设计中设计了乒、乓两个串口数据接收缓存区。

串口寄存器中的数据通过EDMA模式缓存到乒缓存区,当乒缓存区满时,EDMA参数重载,控制切换,将数据缓存至乓缓存区,同时给出EDMA中断,通知CPU读取一帧数据。通过McBSP接口发送数据的过程完全类似。

声码器通过DSP的HPI接口与上层处理器连接,实现数据网分组语音压缩信号的收发。在HPI接口中,设计了以太网数据发送/接收缓存区,并为每个缓存区设计了RP(Read Pointer,读指针)和WP(Write Pointer,写指针),用于控制上层处理器和DSP之间的编码数据交互。同时上层处理器通过HPI接口向声码器发送指令,控制通道的打开或关闭。

3 在媒体网关中的应用设计

声码器内部的主控程序采用定时中断方式访问HPI接口,根据上层处理器的指令打开或关闭通道。同时主程序使用轮询方式处理从E1接口来的PCM话音信号;根据相应的通道工作状态设置编解码算法参数,将话音信号压缩编码;编码后的语音数据,通过HPI接口输出到上层处理器,进入数字网络。使用完全类似的轮询处理方式,逆向处理从来自数字网络的编码数据。

由于数字网络属于分组通信,必须有合适的多媒体实时流网络传输协议以保证语音的连贯性。在声码器的HPI接口控制程序中,设计了一个提供给上层处理器的RTP(Real-time Transport Protocol,实时传输协议)接口,用于完成编码和解码数据包的输出和输入及相应的RTP成帧、解帧功能,具体功能设计如下:

RTP打包和发送:RTP包由具有固定格式的包头和数据部分组成。将编码后的语音数据,按照RTP打包参数的要求组织RTP头和RTP净荷。 RTP包头中的关键字段为SN(Sequence Number,序列号)和TS(Time Stamp,时间戳)。SN用于对RTP包进行排序。每发送一个RTP数据包,SN加1。TS用于标识RTP数据包中第一个字节采样时的时刻,以语音样本为单位递增;对于语音包和静音压缩包,TS增值一致。另外,RTP包头中的PT(Payload Type,负载类型)字段用于指示RTP净荷的数据编码格式。在RFC3550中规定了标准音频载荷类型:G.729编码对应的PT为18。

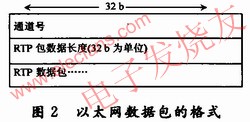

由于RTP包头中没有长度字段,故对RTP包进行了外部扩展:将打好的RTP包作为净荷,附加上RTP包数据长度、通道号,组成“以太网数据包”。针对C6203的32位寻址的HPI总线接口,设计以太网数据包格式如图2所示。

RTP包发送:即写“以太网数据包”至“以太网数据发送缓存区”。首先根据该缓存区的读写指针判断剩余空间;如写空间不够,则放弃此次写操作,该数据包同时被丢弃。如写空间足够,则将数据包写入发送缓存区,并更新写指针。上层处理器根据该缓存区的读写指针判断该缓存区内是否有新数据,并进行读操作,以及更新读指针。

RTP包接收、排序和缓存:分组通信需要考虑语音的防抖动处理。本文通过设置静态抖动缓冲区实现去抖动。首先根据“以太网数据接收缓存区”的读写指针判断是否有新的数据包到来,如果有,则将该数据包根据RTP的SN和TS排列在相应通道的RTP缓存队列中。重复上述过程直至将“以太网数据接收缓存区”中所有的数据包读完,然后更新该缓存区的DSP读指针。对于每个通道的RTP缓存队列,当缓存语音数据到达预先定义的阈值K时,给出标志允许该通道开始进行语音数据解码。如果数据分组有抖动延迟,则解码语音可继续保持K时间单位不被打断。

4 结语

在纯汇编并行优化的基础上设计了高效的G.729ab声码器;利用TMS320C6203的在片外设McBSP实现了连接PSTN的标准E1接口;设计了用于分组数据收发的RTP协议接口,利用TMS320C6203的HPI接口方式与上层处理器连接,使声码器可灵活应用于媒体网关。