马秀飞1,焦杰2,李海滨3,邹德旋1

(1.江苏师范大学 电气工程及自动化学院,江苏 徐州 221116; 2.吉林省广播电视研究所,吉林 长春 130041; 3.吉林省六六一台,吉林 长春 130119)

摘要:收测固定频率的节目信号和全频段频谱扫描是无线调频广播监测工作的主要内容,在实际工作中,这两种功能的实现通常分别使用广播接收监测板卡和频谱监测板卡两种不同的设备。根据这两种不同设备高频接收混频电路的共性与差异,介绍了一种以CPLD为核心,具有两种监测功能的电路,可以根据实际应用的需要设置成为其中任意一个工作模式。这种设计方法具有电路简单、成本低、使用灵活的优点。该电路经过在广播电视监测设备中的实际应用,取得了良好的效果。

关键词:下变频器;CPLD;锁相环

中图分类号:TP37文献标识码:ADOI: 10.19358/j.issn.1674-7720.2017.01.028

引用格式:马秀飞,焦杰,李海滨,等. 调频广播监测设备混频电路的CPLD设计[J].微型机与应用,2017,36(1):93-96.

0引言

无线调频广播监测主要在固定频率上收测节目信号,或者在整个频段内进行频谱扫频。在电路设计上都是采用超外差工作原理,用下变频器把接收信号转换成中频信号[1]。接收信号的频率等于本振频率减去中放电路中心频率的差,通过改变本振频率来改变接收频率。定频收测和扫频两种设备的工作原理相似,只是两者的工作状态不一样。定频收测为了便于精确改变频率,一般采用锁相环[12]设计本机振荡器;而扫频监测采用较快的速度不断变换接收频率,测量出整个频段内各个频率的信号强度,常用以下两种方法设计这种扫频振荡器:

(1)用锁相环设计振荡器,扫频工作就是逐一设定接收频率,测完一个频率信号电平之后再测下一个频率。这种方法的优点是每个测量频率都能准确设置,频率分辨准确[1];还可以任意跳到指定的接收频率,进行随机测量。但是每次设频都会导致锁相环失锁,再次重新捕获锁定需要一个稳定的过程,所以扫频速度较慢。

(2)用锯齿波作为扫描电压,加到压控振荡器上产生本振信号。这种方法的扫频速度快,但是压控振荡器的频率与电压之间并不存在精准的函数关系,不能直接用扫描电压准确换算出振荡频率。因此,在这种扫频式频谱仪上会设计一个可移动的频标,标记出正测量的那个频率值。

另外还有一种采用快速傅里叶变换(FFT)的频谱分析仪,信号经过模/数转换器(ADC)之后,通过傅里叶运算公式计算出各个频率分量而得到频谱曲线。这种方法应用在调频广播频段的高频信号测量时,对模/数转换器和处理器的性能要求较高。广播监测设备受成本限制而基本不采用这种方法。

本文介绍了一种应用在调频广播监测设备中的混频电路,采用CPLD和下变频器芯片设计。在定频收测模式下,用锁相环产生本振信号;在扫频监测模式下,设计了一种带有快速频率测量功能的扫频本振电路。并且还设计了一种带有超时复位功能的SPI接口电路,用于与单片机之间的通信。

1基本电路

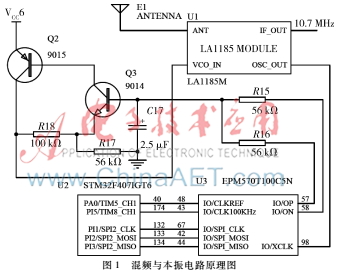

使用型号为EPM570的CPLD进行设计,通过控制混频芯片上的压控振荡器,可以产生不同的振荡频率。定频收测工作模式下的电路是一个锁相环。在扫频模式下工作时,CPLD用PWM方式产生扫频三角波,加在压控振荡器上,再由CPLD测量出瞬时频率。在CPLD中设计了一个SPI接口电路,与STM32F407单片机通信。图1是这部分的电路原理图。

CPLD的57、58管脚输出电压控制信号,经过R15、R16和C17组成的RC低通滤波器,再用Q2、Q3这两个三极管放大,加在LA1185接收电路的压控振荡器[1]VCO_IN上。当控制电压较高时,变容二极管结电容较小,振荡频率较高;而电压较低时,变容二极管结电容比较大,振荡频率较低。

调频广播信号的频率范围在87.5~108 MHz,中频10.7 MHz,所以本振的频率范围是98.2~118.7 MHz。考虑实际生产中器件的差异,设计加在变容二极管上的电压在1~6 V范围内,压控振荡器的实际输出频率范围大约是80~130 MHz。

压控振荡器输出信号送入CPLD的98脚进行鉴频鉴相,同时也实时测量振荡频率。单片机U2使用定时器提供锁相参考时钟CLKREF和一个固定频率的100 kHz时钟。使用SPI接口控制CPLD的工作并读取CPLD中的数据。

2工作原理

电路有两个工作模式,一个是用于监测固定频率信号的定频收测模式,另一个是绘制整个频段内频谱曲线的扫频监测模式。

2.1定频接收工作模式

利用SPI接口可以将电路设置为锁相环工作模式,并获取压控振荡器的振荡频率。图2是这个锁相环的原理框图。

组成锁相环的核心部分是压控振荡器、分频器、鉴频鉴相器(PFD)[2]和低通滤波器。压控振荡器输出的信号经过分频后,用鉴频鉴相器与基准频率进行比较,把频率相位的误差反馈到压控振荡器上。当压控振荡器输出频率f,经过N分频之后恰好与基准频率F相等时,锁相环进入稳定的锁定状态。设置单片机定时器时钟为84 MHz,计数溢出分频系数为M,则有f=N×84/M(MHz)。

需要设定某个振荡频率时,单片机可以利用SPI接口,对CPLD中分频器设置新的分频系数N,并调整定时器溢出数值M即可。为了降低锁相环的相位噪声,要按照两个频率的最简整数比设置N和M。

放大之后的振荡信号同时还送给计数器,实时测量振荡频率,从而检查锁相环的工作状态。这种测频的功能主要用于扫频监测模式。

2.2扫频监测工作模式

在固定的开门时间T之内,用计数器累计待测振荡脉冲数量N,关门时刻用锁存器保存这个数值,同时清零计数器再次启动计数,可以测出振荡频率f=N/T。因为调频广播接收本振的频率大约在100 MHz附近,所以设计频率测量的开门时间为320 μs,用16位二进制计数器,测量的精度可优于10-5。测得的频率数值利用SPI接口送给单片机,再结合检波电路测量得到的信号强度瞬时值就能绘制出频谱曲线。图3是扫频振荡电路的原理框图。

压控振荡器的扫频电压用PWM方式产生。具体就是把100 kHz的基准频率送给计数器计数,并把这个计数器分成高低两组。用数值比较器比较这两组计数数值,根据比较的结果设置输出高低电平就能产生占空比连续改变的PWM信号,再经RC低通滤波器之后即可产生压控振荡器所需要的锯齿波扫描电压。

3CPLD设计

CPLD选用了ALTERA公司的EPM570T100C5N设计同步时序逻辑电路。

3.1分频器的逻辑

设计一种可设置溢出上限的累加器作为锁相环的分频器,它主要由带有同步清零端的同步二进制累加计数器U23、上限数据锁存器U24以及全等数值比较器U26组成。图4是这个分频器的逻辑图。

同步二进制累加计数器U23由12位触发器组成,在压控本振脉冲XCLK的上升沿到达时刻同时翻转,累加计数脉冲数量。12位的上限数据锁存器U24由12个D触发器组成,在SPI_LATCH的上升沿,把从SPI接口收到的D[11..0]的数据值保存起来作为计数上限。全等数值比较器U26把上限锁存器U24和计数器U23的12个数据位逐位进行异或运算之后,再进行12位的或非运算,只有当锁存器与计数器两者数值相同时,比较结果才输出1,下一个时钟边沿将清零计数器。为了防止因各门电路速度差异,导致电路发生部分清零,计数器U23设计了同步清零端SYNC_RESET,所有触发器只在XCLK上升沿同时翻转,保证可靠清零。因为鉴频鉴相器对脉冲边沿特别敏感, 所以用触发器U30锁存数值比较结果,每次溢出,都能产生一个OVERFLOW信号送入鉴频鉴相器。

3.2扫频发生器

把100 kHz的固定频率送给一个17位的计数器进行计数,同时用一个8位数值比较器比较其最高8位和最低8位的数据值,根据比较结果设置PWM输出信号的高低电平。如果低位数值小就输出低电平,低位数值大就输出高电平。再经过低通滤波器就形成了扫频用锯齿波电压。图5所示为这个扫频发生器的逻辑图。

图5扫频发生器逻辑图因为这个低位计数器总是从零累加到255,然后溢出归零,所以设计在它与高位数值相等时把输出置1,它归零时输出也跟着清零。利用这个规律采用全等数值比较器进行设计,既可以简化电路逻辑,又能保证输出端不会因门电路速度差异产生“竞争”与“冒险”。

在17位计数器中,设计8位同步计数器U36作为低8位,9位同步计数器U37作为高9位,并把U37的最高8位与U36的数值送给全等数据比较器U38,两计数值相等时输出高电平脉冲信号,置位触发器U42,然后一直保持1状态直到低位计数器溢出。在U47输出扫频用的PWM信号,再经过外部的RC低通滤波器产生锯齿波扫描电压。

频谱仪通常使用锯齿波作为扫频波形,从最低频率逐渐到达最高频,然后再快速返回最低频开始下一轮扫频。因为PWM输出之后的低通滤波器时间常数较大,如果从最高频率直接返回到最低频率,扫频电压会跟不上变化,产生较大的失真。所以最终采用的是三角波而不是锯齿波。

在三角波扫频情况下,扫频从最低频率逐渐到达最高频率,利用高位计数器U37的溢出信号翻转T触发器U44,选择输出反相信号,使扫频从最高端逐渐返回最低,明显改善了电压频率的跟踪性能。

3.3快速测频逻辑

在CPLD中,用固定开门时间320 μs计数压控本振的脉冲数量,在关门时刻用数据锁存器保存,同时清零计数器,然后再次开门计数。图6是测频电路逻辑图。

外部压控本振信号从XCLK输入16位同步二进制计数器U14,CPLD内部对100 kHz时钟64分频得到的1.562 5 kHz信号从U12送到锁存器U16、U17的时钟端和计数器的异步复位端RESET,在上升沿锁定数据并复位计数器。计数值从U18送到SPI输出电路。

3.4鉴频鉴相器、电荷泵与PWM输出

无论是定频接收模式,还是扫频监测模式,都是对压控振荡器进行控制。在定频接收模式下,利用鉴频鉴相器和电荷泵控制压控振荡器。而在扫频模式下,直接输出PWM。图7所示为这部分的逻辑图。

设置PWMEN为低电平时,电路工作在定频接收模式下。触发器U54、U55和与门U56组成鉴频鉴相器,两个触发器的输出端经三态门U62、U63接到外部的RC电路组成了电荷泵。OP和ON分别是充电与放电引脚。在锁图7鉴频鉴相器、电荷泵与PWM输出逻辑图

定状态,OP和ON都是高阻状态。一旦出现了频率差或相位差,则从OP或ON输出误差脉冲,自动修正本振频率。

设置PWMEN为高电平时,电路工作在扫频模式下,PWM引脚的信号经过三态门控制逻辑在OP和ON输出。

3.5带有超时复位功能的SPI接口

设计SPI接口实现CPU与CPLD通信。图8为SPI接口的逻辑图。

图8具有超时功能的SPI接口逻辑图SPI输入电路就是一个16位的串入并出移位计数器,由U4和U25组成,SPI_CLK上升沿锁存SPI_MOSI数据。SPI输出电路是由U66和U67组成的并入串出移位计数器,对每帧SPI数据都从第二个SPI_CLK下降沿移出一位数据到SPI_MISO。4位二进制计数器U7累加SPI_CLK时钟个数,每计满16个时,产生信号SPI_LATCH通知分频器锁存输入数据。在计数器U7为零时,如果单片机发起SPI数据帧读取,那么U66和U67在SPI_CLK的第一个下降沿锁存并行的SPIDO[15..0],保存最新一次测频结果,经SPI送给单片机。

因为SPI接口是一种同步串行工作接口,如果发生干扰使SPI_CLK上意外多收或少收到一个脉冲,将导致之后的所有数据都发生串位。主要有3种解决方法:(1)多接一条引线,引入外部片选功能,可以复位意外错误;(2)用特殊的数值作为复位命令,例如用实际应用中本不应该出现的0x0000触发复位;(3)用超时检测方法,对未完成的通信数据,超时自动复位。这里采用第3种方法。

在SPI总线空闲时,SPI_CLK为1。超时计数器U3在100 kHz的时钟驱动下,若SPI时钟计数器非零,则累加计数。如果计数期间发生了SPI总线活动,SPI_CLK的低电平可以清零计数器U3,使之不能溢出。如果计数期间SPI总线一直空闲,那么在1.638 4 s后计数器U3溢出,清零SPI时钟计数器U7,从而复位整个SPI接口。

4结束语

如果用几个不同的专用集成电路分别来设计锁相环、扫频电路以及快速测频功能,则需要元件较多。若用单片机来设计这些功能电路,则锁相环功能和快速测频功能都受到单片机IO速度的限制,必须外扩芯片。用CPLD结合单片机是一种结构简单、性价比较高的设计方案。

参考文献

[1] 曾兴雯,刘乃安,陈健.高频电子线路[M].北京:高等教育出版社,2003.

[2] 冠先果,高博,龚敏. 用于锁相环快速锁定的鉴频鉴相器设计[J].电子与封装,2014(5):23-24.