片上众核时代来临,您准备好了吗?

2017-07-14

作者:杨晖

来源:电子技术应用

随着集成电路规模迅速扩大,片上系统进入众核时代。片上众核系统的主要设计挑战是什么?如何定义并优化一个片上众核系统的架构?片上众核系统如何建模和仿真?片上众核系统所遭遇到的可靠性问题如何解决?

面对诸多问题,《电子技术应用》在2017年中国(成都)电子展召开之际,特面向西南地区的听众,举办了“片上众核系统——演进、仿真及可靠性优化设计”技术沙龙,邀请电子科技大学黄乐天副教授和王君实博士为大家答疑解惑。

片上多核系统技术演进与研究现状

黄乐天副教授一直从事片上网络方面的工作,对片上众核系统有深入的研究,他以“片上多核系统技术演进与研究现状”为题,首先从片上众核的诞生和演进入手,对业内两种不同技术路线演进而来的典型片上网络架构——CMP架构和MPSoC架构进入详细的介绍。黄乐天分析了产生两条不同技术路线的原因:

1 起源不同

· CMP起源于通用并行计算机

· MPSoC起源于嵌入式系统设计

2 任务不同

· 通用计算主要任务是求解大型科学问题——单一算法大数据量

· 嵌入式系统主要任务是完成实时处理和控制——多任务协同

3 开发环境不同

· 通用编程模型——易于编程,易于扩展

· 定制化编程模型——特定目的,定制开发

4 优化目标不同

· 通用计算需要尽量提升数据吞吐率/缩短计算时间

· 嵌入式系统需要保证系统实时性

电子科技大学黄乐天副教授

片上众核系统的可靠性设计

片上众核的内部互联、功耗、存储机制、可靠性等问题也使片上众核系统的设计面临诸多挑战。王君实博士的演讲题目为“集成电路的可靠性设计概述”,他以片上网络为例,从故障成因、故障类型、故障层次、容错方法、容错设计等方面进行了详细阐述,提出了提高可靠性的设计方法、检测方法、空间冗余、时间冗余、信息冗余。

电子科技大学王君实博士

自主研发的ESYSim系列片上众核系统EDA工具

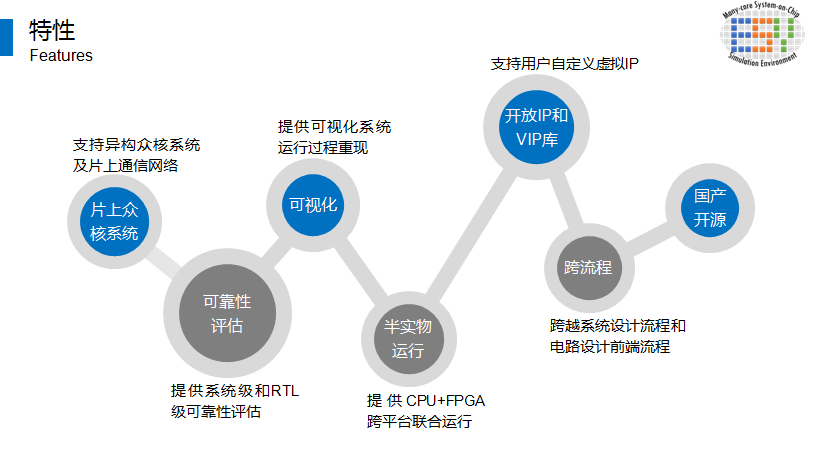

传统电路设计流程已经不能满足苛刻的设计指标和设计周期的限制,电子系统级设计ESL设计方法迅速推广,迫切需要与之配套的EDA仿真工具。国际EDA工具巨头Synopsys和Mentor分别推出了各自的ESL工具,但仍有缺陷。ESYSim由电子科大ESY码农队开发的,是一套国产开源的面向众核片上系统EDA工具,支持异构众核系统及片上通信网络;在系统级和RTL级提供可靠性评估;可视化重现系统运行过程;提供FPGA原型与事务级模型的跨平台实物联合运行。

面向众核片上系统EDA工具——ESYSim的特性

王君实现场以视频和实物展示的形式演示了ESYSim的设计流程:片上网络系统级可靠性评估设计、异构多核系统设计与半实物运行、NoC系统设计流程与数字前端设计流程。

意犹未尽

ESYSim EDA工具将亮相“华为杯”第十二届中国研究生电子设计竞赛,《电子技术应用》祝愿电子科大ESY码农队取得好成绩!