PCIExpress 4.0/5.0测试方法最新更新和市场进展

2019-11-22

来源:是德科技KEYSIGHT

除了成熟的PCIE3.0正在广泛用于终端和SSD存储设备之外,PCIE5.0也已经蓄势待发,除了在今年年中发布Base 1.0规范,近期Base RX夹具也已经上线,提供给会员单位订购:

订购链接

https://pcisig.com/specifications/order-form

图1 PCIE5.0夹具订购表

而当下市场和产业界最翘首期待的PCIE4.0也在今年9月迈出了最坚实的一步。

9月中旬,在上海虹桥万豪大酒店,业界上游公司召集产业界主要系统厂家和测量厂家进行了针对PCIE4.0的第一次Plugfest活动。

Keysight公司作为业界唯一一家提供完整测试方案公司获邀参加,携带了高性能DSAZ594A及UXR0334A实时示波器, M8020A误码仪及 E5071C网络分析仪参加了本次活动。

图2 参会设备不完全照片

通过本次活动结合最近的标准发展情况和其它渠道信息,如下实战经验,今天在这里与大家分享。

发送端(TX)测试

本次活动,针对TX测试,Keysight准备了UXR0334A和Z594A高性能实时示波器。这两台设备均为四通道25GHz带宽以上实时示波器,专门针对System Board测试,特别是需要采用Dual Port测试方法。

图3 PCIE4.0 Phy Test Spec 2.7.5测试项目说明

图4 PCIE4.0 System Board Dual Port测试方法示意图

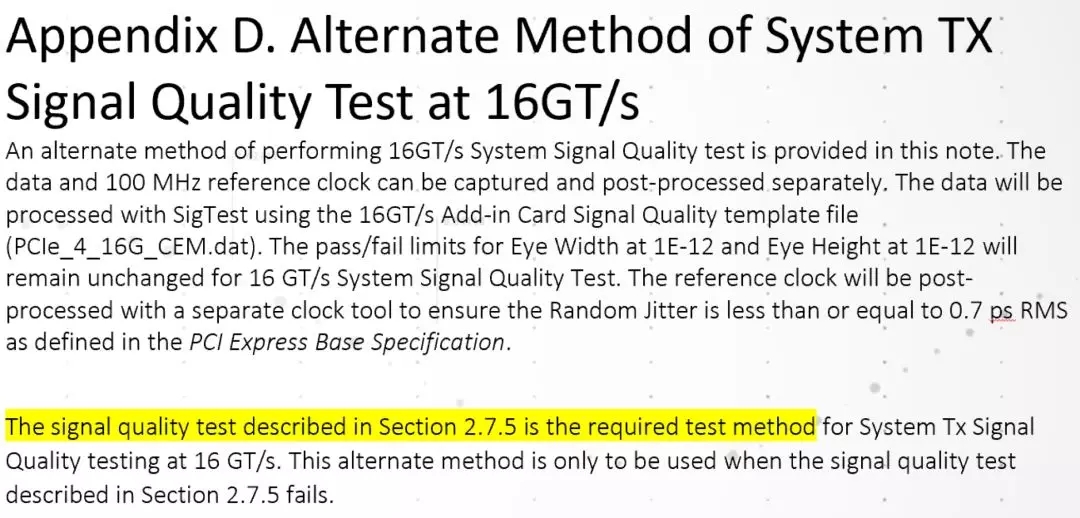

最近也看到很多客户反馈说,在PCIE4.0 Phy Test Spec里,Appendix D有如下描述:

图5 PCIE4.0 Test Spec Appendix D替代方法说明

注意上面黄色高亮文字,明确说明必须采用2.7.5描述方法。只有在采用2.7.5方法测试失败后,才可以采用替代的数据和时钟分开采集再对时钟进行后处理的方法。

因此必须要补充说明的是:

1.双端口测试始终是PCIe 4.0 System Board测试的必须方法。

2.添加了附录D仅作为应急。最初,如果启用了最大SSC,Sigtest会显示问题。开发人员用新方法最近已经解决了Sigtest SSC问题。

3.在最近的WorkShop #110上测试的所有系统板均使用双端口方法进行了测试。

4.双端口方法同时使用时钟和数据测试,基于End Device角度很好地诠释了根组件的信号质量。

5.系统板供应商可以针对参考时钟做抖动平衡或折中,以获得更好的信号抖动,并且仍然符合规范。

接收端(RX)测试

PCIE4.0 RX测试,业界当前有3家厂家号称可以支持,即Keysight公司,X公司和Y公司。

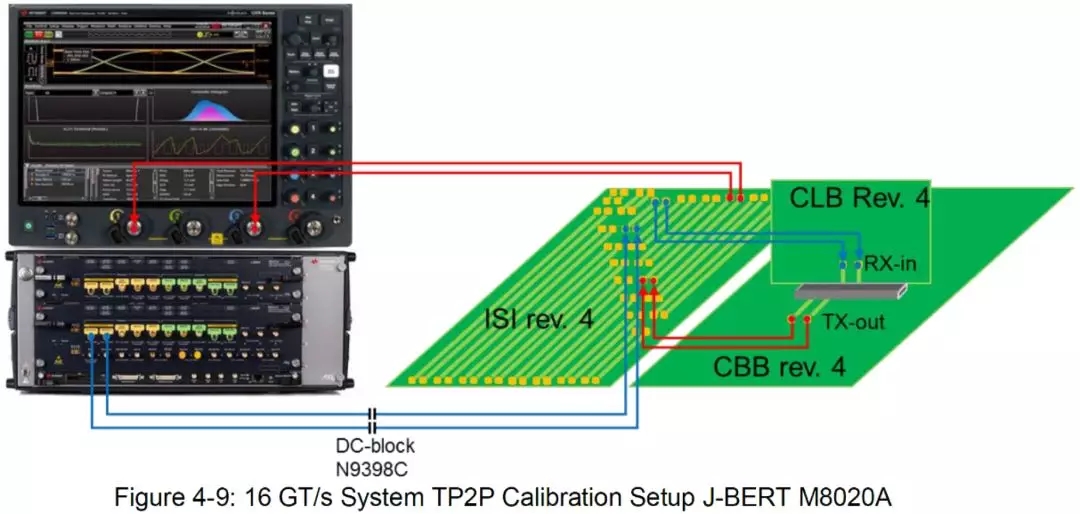

Keysight M8020A误码仪作为本次活动的主力设备,以其业界卓越的集成度带来的简便连接,领先的信号完整性等特点成功圆满完成了本次测试任务。成功地为多个被测设备进行链路协商训练进入环回模式,并顺利进行了误码测试。

而X公司采用的第三方的压力信号校准程序使用较小的抖动(Sj)和干扰(DMI)进行测试。从而导致被测设备未完全经受符合规范的压力信号的抖动容限测试,存在隐患!且针对某些设备在一些链路上不能全部确保链路协商和训练进入环回模式。

Y公司则由于其设备一直未能在业界主流平台上进行过完整的全流程RX测试,因此没有参加本次活动,也就是说在接收端测试上,Y公司已经出局!从近期部分客户反馈和本次活动中也看到,这些客户在采用Y公司设备进行PCIE4.0接收端测试时存在完全不能进入环回状态,因此目前看来深陷泥沼。

ISI夹具标定及链路测试

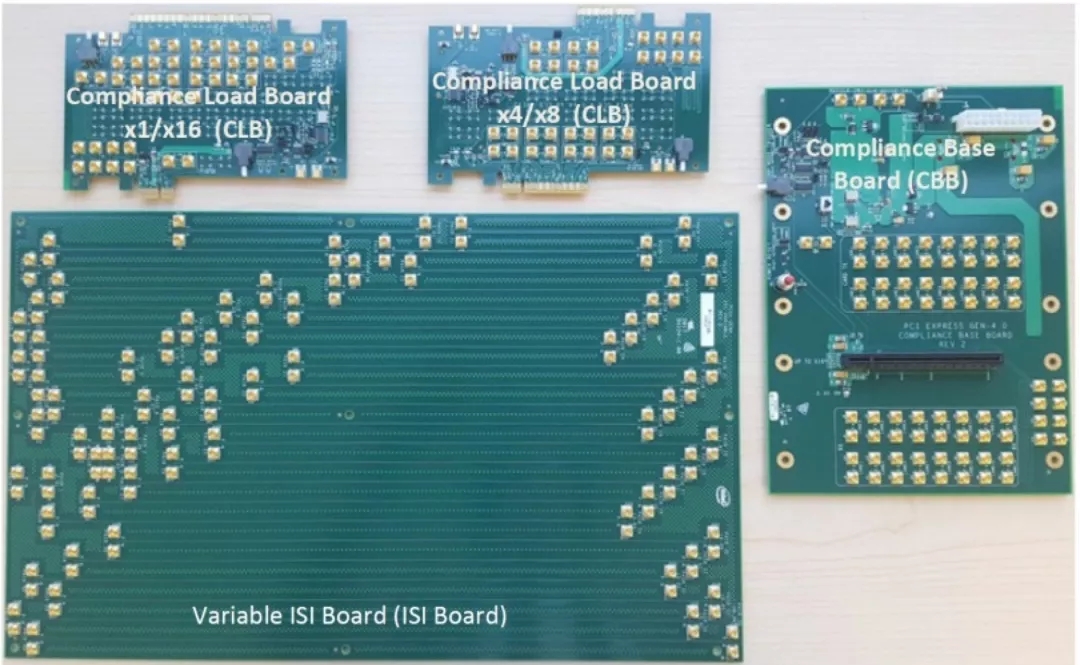

由于PCIE4.0规范里针对信号发送链路强调了全部Insertion Loss需满足不高于 28dB@8GHz,而针对接收链路则强调全部Insertion Loss需满足不高于30dB@8GHz,考虑到不同型号,批次产品和架构以及材质的差异性,为了在测试中满足规范这一要求,PCI-Sig组织为此专门定义并设计了可变ISI夹具板,在板上设计了不同长度尺寸的差分走线配合满足不同材质等情况下全链路的整体损耗要求。

图6 PCIE4.0标准协会夹具

特别是在进行接收端测试之前必须要对注入被测设备的RX端的压力信号进行严格和准确的校准以确保符合规范。如下图针对System Board的RX信号校准示意图。

图7 PCIE4.0 16GT/s System RX Cal示意图

因此在进行RX测试前必须针对包括ISI夹具在内的全链路进行标定并选择总链路损耗在27-30dB。

在参加本次活动之前通常以为采用网络分析仪标定之后即可,通过这次反复插拔活动发现:

反复多次插拔和连接之后夹具上的SMP连接头容易出现过劳和损伤,因此在大批量测试情况下需要不定期采用网络分析仪进行测试标定,目前看来至少1-2周需进行一次标定测试。也就是说,网络分析仪已经成为今天的典型高速标准如PCIExpress4.0研究开发的必备工具。

以上关于最新的PCIE4.0/5.0测试方法更新和最新进展,谢谢阅读!未来将继续更新,欢迎您的持续关注!