大牛解析,FPGA门控时钟原理技术

2020-11-27

来源:芯路芯语

门控时钟的设计初衷是实现FPGA的低功耗设计,本文从什么是门控时钟、门控时钟实现低功耗的原理、推荐的FPGA门控时钟实现这三个角度来分析门控时钟。

一、什么是门控时钟

门控时钟技术(gating clock) 是通过在时钟路径上增加逻辑门对时钟进行控制,使电路的部分逻辑在不需要工作时停止时钟树的翻转,而并不影响原本的逻辑状态。在ASIC和FPGA设计中都存在门控时钟的概念(前者应用更广)。

典型的门控时钟逻辑如下图所示:

二、门控时钟降低功耗的原理

1. FPGA功耗分类

静态功耗:静态功耗又叫泄漏功耗,它是指电路处于等待或不激活状态时-泄漏电流所产生的功耗。通常由FPGA制造工艺的优化而提升。同一代的FPGA产品中,也有专门的低功耗版本(譬如Intel开发的Cyclone10 GX与Cyclone 10 LP,后者为低功耗版本low power但前者性能更强)。可以在FPGA选型时加以考虑。

动态功耗:是指电容充放电功耗和短路功耗,是由电路的翻转造成的。FPGA中的动态功耗主要体现在元件的电平翻转时对负载电容的充放电及时钟的翻转。

2. 为什么门控时钟可以降低功耗

当系统中某模块电路完成既定任务后(譬如TDC中对BIN的标定等初始化类任务),通过门控时钟使能信号的控制,使得驱动该模块的时钟停止翻转,相应的时序元件不再更新,那么其间的组合逻辑也恢复到静态。此时该模块的功耗相当于静态功耗,从而降低了整个系统的功耗。

三、不合理的门控时钟设计

1.伪门控时钟

如下图所示,设计中有意识地使用使能信号,意图维持寄存器的数据。但是仅对寄存器组的数据输入端添加选择器和使能信号,并不妨碍寄存器组时钟输入端的翻转,输出维持不变只是因为存在反馈回路在不断的进行使能判断、输出、使能判断、输出的循环。实则并没有起到低功耗的作用。

当然某些情况下确实需要用到这种设计,此处仅用来和门控时钟做区分,避免混淆。

2.直接门控时钟

将使能信号直接连接在AND门,结构简单。不足之处在于产生使能信号的组合逻辑的毛刺将完全地反应到AND门,造成门控时钟输出质量变差(clk_en将会有占空比不良和毛刺等情况)。

四、推荐的门控时钟设计

1.基于锁存器的门控时钟

锁存器是电平敏感的元件,此图中当CLK信号为低电平时,锁存器透明,EN端数据直接传输至AND门的一端(ENL),AND门另一端连接CLK。

当产生使能信号的组合逻辑不复杂时,产生使能信号的时间小于半个时钟周期。在CLK高电平时,锁存器的引入有效地过滤了前段组合逻辑竞争冒险产生的毛刺;在时钟低电平时,前段组合逻辑的毛刺将受到AND门控制将无法输出。较好地实现了门控时钟的要求。

当产生使能信号的组合逻辑复杂时,产生使能信号的时间大于半个时钟周期。考虑锁存器的延时,那么对于首个ENCLK周期而言,占空比将被削减;当EN信号拉低时,则有可能产生毛刺。均不利于后续寄存器组的时序过程。

这种情况难以通过在锁存器前端加同步寄存器避免,因为此时的使能信号是不满足寄存器的建立时间的,大概率会产生亚稳态现象。因此产生门控使能信号的组合逻辑应当尽可能简化,保证在半个时钟周期之内得到稳定电平。

保险起见,一方面,保证使能信号半周期确定;另一方面,在锁存器之前加一级上升沿触发的寄存器,过滤输入锁存器的信号。

2.基于寄存器的门控时钟

上面介绍的基于锁存器的门控时钟实际上更适合在ASIC中实现,一方面FPGA中没有专门的锁存器资源,需要利用其中的组合逻辑资源外加寄存器来等效地实现,不经济;另一方面,锁存器本身的特性没法进行静态时序分析,出问题了不易排查。

真正适合在FPGA中实现的是基于寄存器的门控时钟,如下图所示。

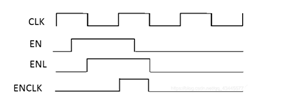

前段使用加法器产生计数值,通过比较器产生使能信号,送入使能寄存器。值得注意的是,前端产生使能逻辑时序元件是上升沿触发,而使能寄存器是下降沿触发。如此一来,同样需要满足产生使能信号的组合逻辑简单这一前提要求(半周期内达到en寄存器的建立时间)。好处在于,AND门时时刻刻都只有一个输入在变,不容易产生毛刺。时序图如下:

为了便于理解,此处给出若使能寄存器也是上升沿触发的时序图:

可见,AND门变化时两个个输入在变,容易产生毛刺。

五、讨论

只有当FPGA工程需要大量降低功耗时才有必要引入门控时钟,若必须引入门控时钟,则推荐使用基于寄存器的门控时钟设计。

在时钟树的枝干处使用门控,而不是在枝丫处使用门控。

使用门控时,应该注意时钟的质量(使用专用时钟网络),毕竟好的时钟才能产生好的使能信号和门控时钟信号。同时,产生使能信号的逻辑不能太复杂,确保可以满足使能寄存器的建立时间和保持时间。

与或门控输出的时钟信号,需要在timeanalyzer中设置为base clock。否则将会引入人为的时钟偏斜。如下,将会以没有使能寄存器的门控路径作为最短分析路径,以有寄存器的路径作为最长路径分析。

类似地,产生门控时钟信号最好只有一个两输入AND门(OR门)。附加逻辑越多,产生毛刺可能性越大。