1nm需要怎样的光刻机?ASML是这样说的!

2020-11-30

来源:半导体行业观察

比利时的独立半导体高科技研究机构——imec每年都会在东京举办“imec Technology Forum(ITF) Japan”,并介绍他们的年度研发成果,今年考虑到新冠肺炎的蔓延,于11月18日在线举行。

首先,imec的CEO兼总裁Luc Van den hove先生做了主题演讲并介绍了imec的整体研究内容,并强调指出,imec通过与ASML通力合作研发并实现新一代高解析度EUV曝光技术(高NA EUV Lithography),促使摩尔定律继续发挥作用,且即使工艺微缩化达到1纳米后,摩尔定律也会继续存在。

CEO兼总裁Luc Van den hove先生在ITF Japan 2020上做主题演讲。强调“摩尔定律不会总结”。(图片出自:笔者在ITF Japan 2020上的截图)

不仅是日本半导体企业,其他很多半导体企业也都认为“摩尔定律已经终结”、“成本高、收益低”,因此相继放弃研发工艺的微缩化,imec始终提倡为摩尔定律续命,因此是当下全球最尖端的微缩化研究机构。

日本的曝光设备厂家也在研发阶段放弃了EUV曝光技术(这对实现超微缩化是必须的),而imec和ASML合作拿公司的命运做赌注,时至今日一直在研发 。

Imec公布了1纳米以后的逻辑半元件的技术蓝图

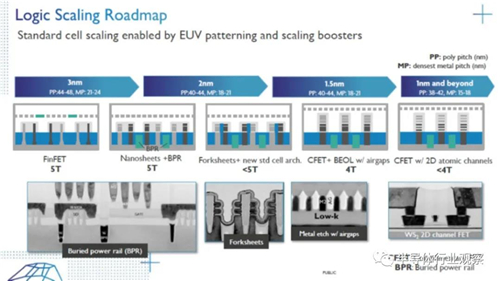

Imec在ITF Japan 2020上公布了3纳米、2纳米、1.5纳米以及1纳米及后续的逻辑元件的技术蓝图。

Imec的逻辑元件的微缩化技术蓝图。(图片出自:ITF Japan 2020上的演讲资料)

第一行的技术节点(Node)名下面记录的PP为Poly-silicon排线的中心跨距(Pitch,nm),MP为金属排线的中心跨距(Pitch,nm)。此处,我们需要注意的是,以往的技术节点指的是最小加工尺寸、栅极(Gate)的长度,如今不再指某个特定场所的物理长度,而是一个符号。

此处的展示的采用了BPR、CFET、2D材料的沟槽(Channel)结构以及材料已经在别处的演讲中提及。

EUV的高NA化对于进一步实现微缩化至关重要

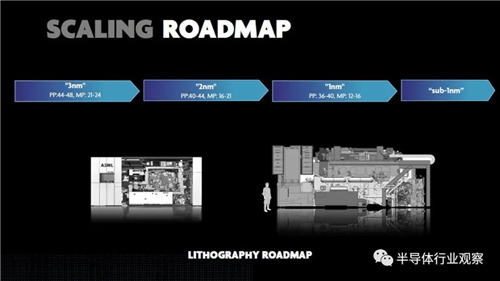

TSMC和三星电子从7纳米开始在一部分工程中导入了NA=0.33的EUV曝光设备,也逐步在5纳米工艺中导入,据说,2纳米以后的超微缩工艺需要更高解析度的曝光设备、更高的NA化(NA=0.55)。

随着逻辑元件工艺微缩化的发展,EUV曝光设备的技术蓝图。(图片出自:ITF Japan 2020上的演讲资料)

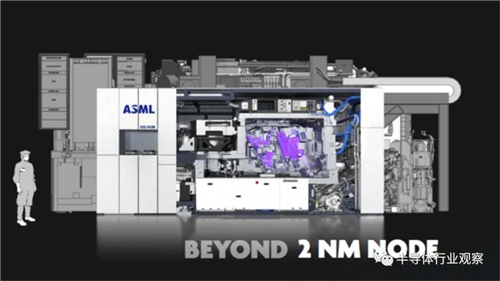

ASML已经完成了高NA EUV曝光设备的基本设计(即NXE:5000系列),预计在2022年前后实现商业化。这款新型设备由于光学方面实现了大型化,因此尺寸较大,据说可达到以往洁净室(Clean Room)的天花板。

现有的、用于量产的EUV曝光设备(NA=0.33,前图)和新一代的高NA EUV曝光设备(NA=0.55,后图)的尺寸的比较。(图片出自:ITF Japan 2020上的演讲资料)

一直以来,ASML都和imec以合作的形式研发光刻技术,为了推进采用了高NA EUV曝光设备的光刻工艺的研发,imec在公司内新设立了“IMEC-ASML HIGH NA EUV LAB”,以共同研发,且计划和材料厂家共同研发光掩模(Mask)、光刻胶(Resist)等材料。

ASML-IMEC的高NA EUV研究中心的印象图。(图片出自:ITF Japan 2020上的演讲资料)

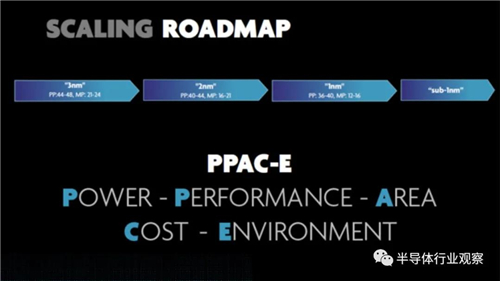

最后,Van den hove先生表示未来会继续推进微缩化:“实现逻辑元件工艺微缩化的目的在于俗称的PPAC,即Power(功耗)的削减、Performance(电气性能)的提高、Area(空间面积)的缩小、Cost(成本)的削减。当微缩化从3纳米、2纳米、1.5纳米发展到1纳米以后,即发展到Sub-1纳米的时候,需要考虑的因素不仅是以上四项,还有环境(Environment)因素,希望未来继续发展适用于可持续发展社会的微缩化工艺。”

在工艺微缩化过程中,不仅重视以往的PPAC,还增加了E(环境),即PPAC-E。(图片出自:ITF Japan 2020上的演讲资料)