三星公布3纳米芯片的更多细节

2021-03-12

来源:半导体行业观察

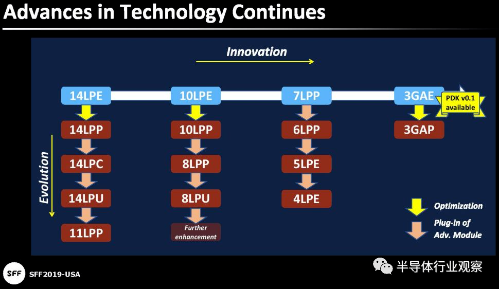

三星晶圆厂将成为第一家在即将到来的3nm工艺中使用类似全栅场效应晶体管(GAAFET)结构的半导体制造商。虽然该节点尚未准备就绪,但在IEEE国际固态电路会议(ISSCC)上,三星晶圆厂的工程师分享了有关即将推出的3 nm GAE MBCFET(multi-bridge channel FET)制造技术的一些细节。

据介绍,有两种类型的GAAFET:典型的GAAFET,这被称为具有“薄”鳍的纳米线。以及MBCFET,称为具有“厚”鳍的纳米片。在两种情况下,栅极材料在所有侧面上都围绕沟道区。纳米线和纳米片的实际实现方式在很大程度上取决于设计,因此,一般而言,许多行业观察家用术语GAAFET来描述两者。但是以前它们被称为环绕栅晶体管(surrounding-gate transistors :SGT)。值得一提的是,MBCFET是 三星的 商标。

(图片来源:三星)

1988年,全球首次展示了GAAFET,因此该技术的关键优势众所周知。这种晶体管的结构使得设计人员可以通过调节晶体管通道的宽度(也称为有效宽度或Weff)来精确地对其进行调谐,以实现高性能或低功耗。较宽的薄片(sheets)可以在更高的功率下实现更高的性能,而较薄/较窄的薄片可以降低功耗和性能。为了对FinFET做类似的事情,工程师必须使用额外的鳍来改善性能。但是在这种情况下,晶体管沟道的“宽度”只能增加一倍或两倍,这并不是很精确,有时效率很低。另外,由于不同的晶体管可以用于不同的目的,因此通过调整GAAFET可以提高晶体管的密度。

(图片来源:三星)

早在2019年,三星推出的的3GAE工艺设计套件版本0.1就包括四种不同的纳米片宽度,以为早期采用者提供一定的灵活性,尽管目前尚不清楚该公司是否增加了宽度以提供额外的灵活性。但是三星表示,总的来说,与7LPP技术相比,其3GAE节点将使性能提高30%(在相同的功率和复杂度下),功耗降低50%(在相同的时钟和复杂度下),并且晶体管密度提高了80%(包括逻辑和SRAM晶体管的混合)。

(图片来源:三星)

三星的3GAE(其第一代MBCFET技术)将于2022年推出。虽然三星目前尚未披露其所有特性。但该公司在ISSCC上讨论了如何使用新型晶体管来提高SRAM性能和可扩展性。

近年来,SRAM的可扩展性一直落后于逻辑的可扩展性。同时,现代片上系统将SRAM的负载用于各种高速缓存,因此提高其可伸缩性是一项至关重要的任务。

(图片来源:三星)

据《EE Times》亚洲报道,三星代工厂在ISSCC上介绍了其256Mb MBCFET SRAM芯片,该芯片的尺寸为56mm2 。这意味着尽管该公司尚未推出其首款3GAE逻辑芯片,但显然该技术适用于SRAM。

SRAM是一个六晶体管存储单元:两个传输门(pass gates),两个上拉和两个下拉。在FinFET设计中,SRAM单元将使用具有相同沟道宽度的相同晶体管。借助MBCFET,三星可以调整沟道宽度,因此提出了两种方案:在一种情况下,三星将沟道更宽的晶体管用于传输门和下拉电路,而在另一种情况下,三星将使用具有较宽沟道的晶体管用于传输门和晶体管。

至于较窄的下拉通道。三星通过IEEE Spectrum称,通过将具有更宽沟道的晶体管用于传输门,并将具有较窄通道的晶体管用于上拉,与常规的SRAM单元相比,三星设法将写入电压降低了230 mV 。