三星推新工艺,将FinFET带到28nm,首攻CIS堆叠?

2021-10-08

来源:半导体行业观察

尽管大多数关于芯片制造的讨论都集中在行业的前沿和极快且复杂的方面,但现在,对“传统”工艺技术的需求比以往任何时候都高,而且数量也比最新和最好的要大得多。这些传统工艺构成了大多数现代电子产品的支柱,因此能够以更低的成本/功耗提供同等技术对于制造商和芯片设计人员来说通常是双赢的。

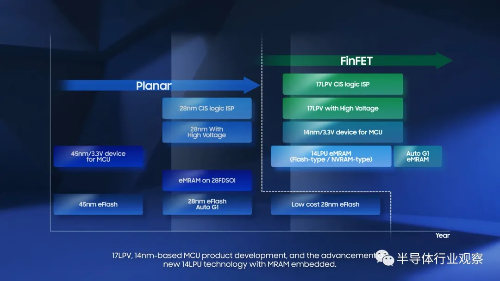

为此,三星宣布推出新的 17 纳米工艺节点,专为仍在使用平面 28 纳米工艺但希望利用 14 纳米 FinFET 技术的客户而设计。

在现代处理器设计中,制造工艺节点带有一组设计规则。要在该节点上设计芯片,它必须遵循这些设计规则。通常这些规则会有绝对的最坏情况限制,但如果芯片设计人员可以利用这些限制来优化他们的产品,那么熟悉什么可以做或不可以做是有好处的。

因此,像三星 28 纳米这样使用平面晶体管的工艺,将有一套不同于三星使用 3D FinFET 晶体管的 14 纳米的设计规则。设计规则还考虑了将电源放置在何处、连接性、从晶体管到用于封装的接触焊盘的金属堆叠。

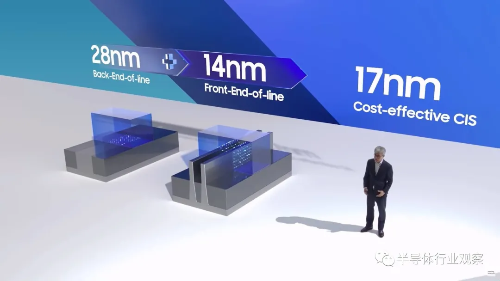

在制造方面,从高层次上讲,有两三个主要部分需要考虑。生产线前端 (FEOL) 是电路制造、设计晶体管的起点。当我们谈论前沿技术时,它是内在应用的 FEOL 部分,因为我们需要越来越好的工具来在硅中制造越来越小的细节,以获得最好的晶体管。一旦 FEOL 用晶体管完成了许多层,晶圆就会移动到线路后端 (BEOL) 以用于其余电路——BEOL 负责放置连接线层、电源层和所有辅助连接。BEOL 之后,芯片将进行测试、切割(划片)和封装。

有时,术语中间线或中间线末端 (MEOL) 用于具有专为多芯片堆叠设计的硅通孔 (TSV) 的芯片。

在整体层面上,任何工艺节点(例如 28nm)的 FEOL 和 BEOL 都有针对这两个细分市场的 28nm 版本设计规则。有时,制造商会将 FEOL 上的一套设计规则与 BEOL 上的另一套设计规则结合起来,以生产具有两者的某些功能的新产品线。这就是三星在三星代工论坛宣布的新 17nm / 17LPV(低功耗值)工艺正在做的事情。

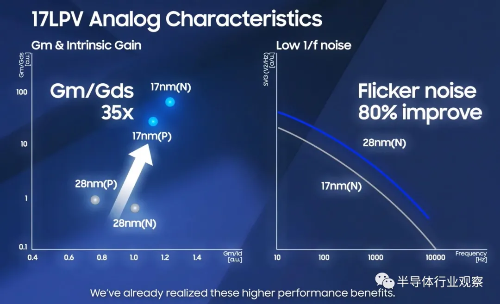

17LPV 将结合 14nm FEOL,有效地将 14nm FinFET 晶体管与 28nm BEOL 进行连接。这意味着客户可以以额外的成本获得 FinFET 设计的性能/功率优势,而无需支付更高密度的 BEOL 的额外成本。最终,芯片尺寸可能仍由较大的节点 BEOL 决定,但似乎需要较低功率的晶体管。

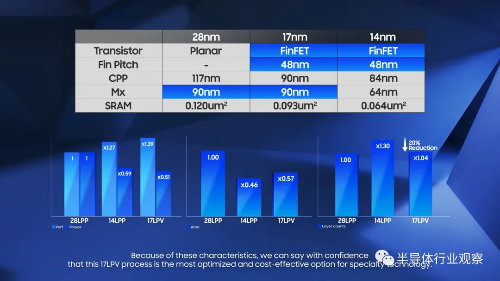

三星声称,与传统的 28 纳米工艺相比,17LPV 的芯片面积将减少 43% 以上,性能提高 39%,或功率效率提高 49%。

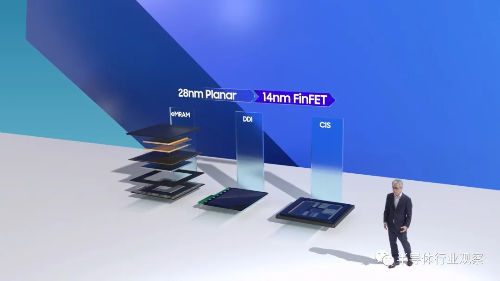

17LPV 的第一个应用将是相机图像信号处理器,作为三星 CMOS 图像传感器产品组合的一部分。这些芯片不一定需要密度,这使得 17LPV 非常适合,但优化的功率和成本将使涉及堆叠的专业技术受益。

除此之外,三星正在将 17LPV 集成到其高压产品中,针对需要后端高压支持并结合逻辑改进的 DDIC/显示驱动器。

除了 17LPV,三星代工厂正在创造 14LPU(我们认为这仍然是 28nm BEOL + 14nm FEOL)或 Low Power Ultimate,用于嵌入式 MRAM 和微控制器。

这个新节点的确切时间尺度目前尚未披露,尽管三星代工厂的代表在为这些市场开发新的专业工艺解决方案时称该节点是公司内部“范式转变”的一部分。