英飞凌推出全新的OptiMOS™源极底置功率MOSFET

2022-02-16

来源:英飞凌

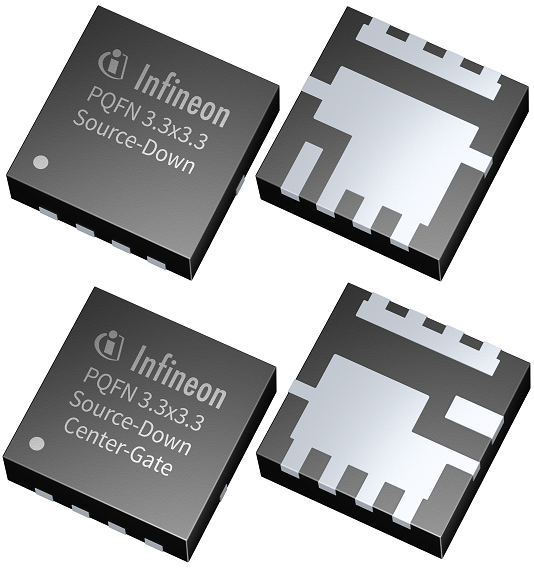

【2022年2月15日,德国慕尼黑讯】高功率密度、出色的性能和易用性是当前电源系统设计的关键要求。为此,英飞凌科技股份公司(FSE: IFX / OTCQX: IFNNY)推出了新一代OptiMOS™ 源极底置(Source-Down,简称SD)功率MOSFET,为解决终端应用中的设计挑战提供切实可行的解决方案。该功率MOSFET采用PQFN 封装,尺寸为3.3 x 3.3 mm2,支持从25 V到100 V的宽电压范围。此种封装可实现更高的效率、更高的功率密度以及业内领先的热性能指标,并降低BOM成本,在功率MOSFET的性能方面树立了新的行业标杆。该器件的应用领域十分广泛,涵盖电机驱动,适用于服务器、电信和OR-ing的SMPS,以及电池管理系统等。

与传统的漏极底置(Drain-Down)封装相比,最新的源极底置封装技术能够让器件的外形尺寸接近于裸芯片。此外,这种创新封装技术还能降低损耗,进一步增强器件的整体性能。相较于最先进的漏极底置封装,采用源极底置封装可使RDS(on)降低30%。这一技术创新能够为系统设计带来的主要优势包括:缩小外形尺寸,从SuperSO8 5 x 6 mm2封装转变到PQFN 3.3 x 3.3 mm2封装,可减少约65%的占位空间,让可用空间得到更有效的利用,从而提高终端系统的功率密度和系统效率。

此外,在源极底置封装中,热量通过导热垫传递到PCB上,而非通过内部引线键合或铜夹带设计,以此来改善散热效果。这也使得结-壳热阻(RthJC)从1.8K/W降到了1.4K/W,降幅超过20%,从而能够实现优异的热性能。英飞凌目前推出的两个型号占板面积不同,它们分别是SD标准门极布局和SD门极居中布局。在标准门极布局中,电气连接的位置保持不变,方便将标准的漏极底置封装简单直接地替换成新的源极底置封装;而在中央门极布局封装中,门极引脚被移到中心位置以便于多个MOSFET并联。这两种型号都能够优化PCB布局,使得寄生效应降低,PCB损耗改进,且易于使用。

供货情况

OptiMOS™ 源极底置功率MOSFET现已开始供货,其采用PQFN 3.3 x 3.3 mm2封装,支持从25 V到100 V的宽电压范围,目前推出的两个型号占板面积不同。