VLSI 2022亮点总结:中国大陆不可忽视!

2022-06-22

作者:李飞

来源:半导体行业观察

IEEE Symposium on VLSI Technology and Circuits(超大规模集成工艺与电路大会)是全球半导体行业与ISSCC齐名的最重要会议,每年都会有来自半导体业界和学术界最顶尖的研究成果发表,从这些研究成果中也可以看到全球半导体行业的发展。今年的VLSI会议刚刚于上周落下帷幕,本文将给大家带来这届会议上的亮点总结。

Nvidia:AI与高性能计算是两大主题

Nvidia作为数据中心和人工智能领域领跑的公司,事实上在VLSI这类集成电路相关的会议上发表论文并不多,而关于其人工智能芯片的对应技术发表就更少了。而这次VLSI会议上,Nvidia则是发表了两篇论文,其中一篇正是和人工智能相关,这也就成为了大众关注的热点。

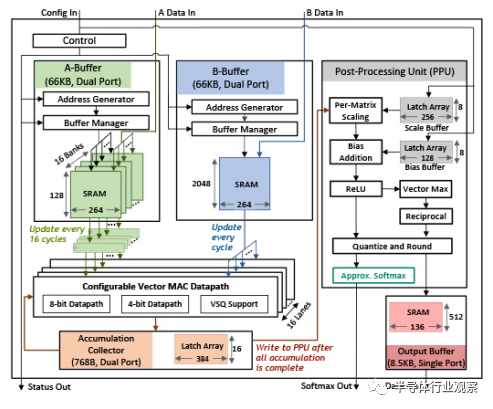

这篇Nvidia发表的人工智能加速芯片相关的论文标题为“A 17-95.6 TOPS/W Deep Learning Inference Accelerator with Per-Vector Scaled 4- bit Quantization for Transformers in 5nm”,其主要内容是讨论了如何针对下一代神经网络模型(即Transformer)做推理相关的优化。人工智能领域,在以卷积神经网络为代表的模型占据主流地位十多年之后,下一代的神经模型网络即Transformer正在自然语言处理、图像识别等任务上显示出重要的潜力,有望在性能上超过卷积神经网络——事实上在自然语言处理领域,Transformer已经是标准的神经网络模型了。同时,Transformer的计算量很大,也对推理加速芯片提出了新的要求。而在AI芯片推理加速领域,针对Transformer做优化的工作并不如当年针对卷积神经网络这么多,主要原因是卷积神经网络中可以通过各种数据复用技术来实现相当高的效率提升,但是在Transformer模型上这些技术并不是很有用。

在Nvidia发表的这篇论文中,我们看到了Nvidia在这方面的研发思路,就是软硬件结合。在神经网络加速芯片领域,一直有两种思路,第一种是走纯硬件优化的道路,即完全通过数据流和电路的优化,在完全不更改模型的情况下来实现计算的加速,这样的优化最后得到的模型输出理论上应该和原模型数学上完全等价,同时对于设计者来说也无需理解模型的训练和设计过程,只需懂硬件执行即可。另一条道路则是软硬件协同设计,即在设计加速芯片的同时也对模型做一定程度的更改,在对模型不产生重大精度损失的前提下让模型对于硬件更有友好。这也就需要设计团队同时能精通模型和硬件,即对于团队有更高的要求。Nvidia的这篇论文走的就是后者,其主要的优化在于首先对于Transformer做激进的量化,把计算精度减少到4比特,从而大大减少对于内存的压力,也减少计算通路的面积以及能量消耗。另一个重要优化则是算符的优化,把本来硬件开销很大的softmax操作用对于硬件较为友好的近似形式来取代,从而大大减少了开销。通过这样的软硬件协同设计,尤其是拥有强大的算法团队,该Transformer加速芯片可以实现极高的能效比(95.6 TOPS/W),同时模型精度与原来的模型几乎一致。

值得注意的是,在Nvidia下一代GPU Hopper架构中,这样的Transformer专属加速模块也是一个重要的新特性。我们认为Nvidia在这篇论文中发表的优化手段很有可能已经在Hopper系列GPU中产品化。

除了这篇关于Transformer的加速芯片论文之外,Nvidia另一篇论文是关于超高速数据互联电路,题为“A 0.297-pJ/bit 50.4-Gb/s/wire Inverter-Based Short-Reach Simultaneous Bidirectional Transceiver for Die-to-Die Interface in 5nm CMOS”,其主要是针对在Silicon Interposer上的短距离超高速数据互联,可以实现同时双向数据互传。该论文也和Nvidia在高级封装领域的一贯投入相吻合,主要针对的是使用高级封装技术来实现计算的可扩展性,从而为高性能计算的性能提升铺平道路。

Intel:下一代半导体工艺与封装技术

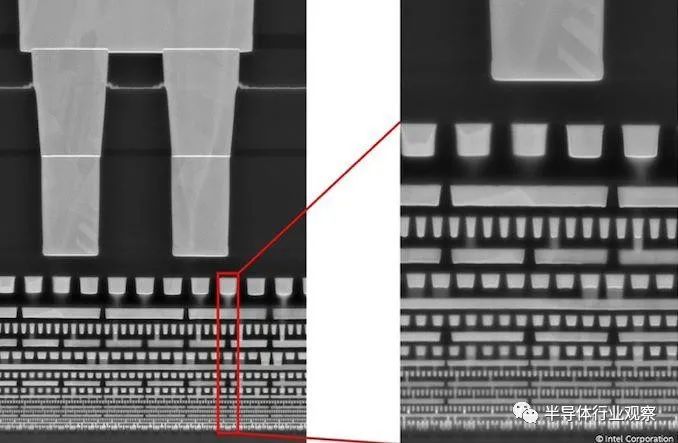

Intel在这次VLSI 2022会议上最大的亮点无疑是公布了下一代工艺Intel 4的细节(论文标题为“Intel 4 CMOS Technology Featuring Advanced FinFET Transistors optimized for High Density and High-Performance Computing”)。Intel 4将会是Intel第一个使用EUV技术的工艺节点,而根据Intel公布的数据,使用EUV也为Intel 4带来了显著的提升,例如Intel 4的工艺步骤大大减少,光罩数量相对上一代Intel 7下降了20%(这也表示大大降低了成本),同时Intel也表示EUV带来了良率的提升(应当与工艺步骤减少相关)。

在集成度方面,Intel对于Intel 4的数字是集成度相当于Intel 7提升两倍,具体来说Fin之间的间距较少了12%,底层金属间距减少了25%,标准单元的高度降低了41%,从面积上来说则是标准单元的面积减少了50%。当然这主要是针对逻辑单元来说,SRAM的集成度提升在25%左右,并不到两倍。

在性能方面,Intel 4相对上一代工艺Intel 7在相同功耗的情况下可以把性能(时钟频率)提高22%,而在相同时钟频率的情况下则可以把功耗减少40%。这样的性能提升是一个很不错的数字,我们认为结合其集成度方面的提升,Intel 4是一个值得期待的工艺节点。有意思的是,Intel同时在本届VLSI会议上发表了一款使用Intel 4工艺的芯片,论文题为“An 8-core RISC-V Processor with Compute near Last Level Cache in Intel 4 CMOS”,这里也可以看到Intel在RISC-V领域的投入,把最新的RISC-V生态搭配其最新的Intel 4工艺,可望在未来实现Intel在处理器领域的新战略布局。除了RISC-V CPU之外,Intel还在本届VLSI会议上发布了一系列使用Intel 4工艺的电路,包括AES加密引擎,SRAM IP和温度传感器等等。

除了下一代半导体工艺之外,Intel在VLSI 2022上最值得注意的成果是下一代封装技术。相关方面有两篇论文,一篇是使用光互连接口的FPGA,该研究成果把FPGA和光通信PHY使用芯片粒技术封装在一起,从而可以实现5.12Tbps的超高速芯片间互联,有机会能成为芯片粒之间超高带宽数据互联的新范式。除此之外,另一篇Intel的论文讨论了一个高级封装系统中的重要部分即电源管理,在该论文中Intel提出了一种专门为TSV 3D封装系统设计的buck电源管理系统,通过利用高级封装技术(如把电感集成在封装里面)大大提升了电源输出的性能。从这些论文我们也可以看到Intel在高级封装技术领域的投入,未来可望会成为和半导体工艺一起成为Intel的新技术引擎。

三星:多条战线全面布局

与Nvidia专注于人工智能和高性能计算,Intel主打下一代半导体工艺和高级封装不同,三星在本届VLSI会议上发表的研究成果可谓是契合其一向的战略,即各条战线全面布局。

首先,三星仍然以存储器为投入最大的方向。在下一代DRAM的竞争中,三星一直处于领先的地位,在之前就宣布要率先发布HBM3接口的DRAM,而这次在VLSI 2022上,三星就发布了相关的研究成果,基于其最新一代10nm DRAM技术,结合TSV 3D封装和优化过的纠错码技术(ECC),其16 GB DRAM在HBM3接口上实现了1024 GB/s的超高带宽,而这篇论文也可以看作是三星在内存领域对其能力的一次展示。

除了DRAM之外,三星还在嵌入式Flash、先进工艺的标准单元设计、图像传感器、无线收发机、LiDAR等领域有研究成果发表,由此充分可见其在半导体领域多中心战略。

中国大陆:不可忽视的力量

随着中国大陆半导体行业的发展,本届VLSI大会上来自中国大陆的论文数量不容忽视。其中,最值得关注的是华为和中科院联合完成的使用IGZO器件作为下一代DRAM的研究论文,标题为“Vertical Channel-All-Around (CAA) IGZO FET less than 50nm CD with High Read Current of 32.8μA/μm (Vth +1V), Well-Performed Thermal Stability up to 120°C for Low Latency, High-Density 2T0C 3D DRAM Application”。该论文使用了垂直channel-all-around技术,可以实现超高集成度(有源面积小于50x50nm2),且具有很高的导通电流密度和非常好的亚阈值关断特性。该研究将为下一代高密度、高性能3D DRAM铺平道路。该论文也登上了VLSI 2022亮点论文的列表,表示该研究获得了半导体业界的高度肯定。事实上,在IGZO领域中国大陆已经走在了领先的位置;在IGZO总共五篇论文中,来自中国大陆的论文有三篇。除了前述的华为和中科院合作的IGZO DRAM论文外,另有一篇中科院和华为合作关于IGZO DRAM器件中TZI和BTI效应建模的论文,以及一篇由中科院独立研发使用了双栅极结构把IGZO晶体管沟道长度缩短至30nm并实现极佳器件性能(其中跨导和DIBL都打破了目前的世界记录)。另外,中科院在用于人工智能的新存储器领域也有很大收获,有两篇相关的基于新存储器件的论文发表。除了中科院之外,中国大陆还有北大、清华、浙大、华东师范大学等来自高校的论文在本届VLSI上发表。

除了科研单位之外,中国半导体业界这次也有不少论文在VLSI大会发表。除了前述来自华为的论文之外,还有来自睿科微的论文“Highly Reliable 40nm Embedded Dual-Interface-Switching RRAM Technology for Display Driver IC Applications”。该论文主要提出了一种使用RRAM来取代传统SRAM来完成AMOLED屏幕中实现屏幕矫正(demura),从而实现比传统SRAM更低的成本,更高的性能和更好的能效比。睿科微是兆易创新和RAMBUS在合肥建立的合资公司,致力于将RRAM技术商业化,而这次在VLSI大会上发表的论文则显示睿科微在这个技术方向上有了长足的发展,实现了重要的里程碑。

综合来看,中国大陆无论是高校还是业界都在本届VLSI大会上发表了高质量的论文,这也是中国大陆半导体行业发展的重要标志。