3nm先发优势能让三星超越台积电吗?

2022-07-01

来源: TechSugar

三星电子官宣,基于3nm全环绕栅极(Gate-All-Around,简称 GAA)制程工艺节点的芯片已经开始于韩国华城工厂初步生产。这也意味着,三星抢先台积电成为全球首家实现3nm芯片量产的公司,以先发优势率先拿下3nm芯片市场。

三星电子表示,其3nm芯片在全球范围内首次采用了MBCFET(Multi-Bridge-Channel,多桥通道晶体管)技术,突破了FinFET技术的性能限制。该技术基于GAA晶体管架构,通过降低工作电压水平并增加驱动电流,有效提高了芯片性能及能耗比。

相较于三星5nm工艺而言,采用GAA晶体管的3nm工艺,在性能上提高了23%,功耗降低了45%,芯片面积减少16%。除了应用于高性能、低功耗计算领域,三星电子还计划将3nm工艺扩展至移动处理器领域。

三星电子高管展示3nm半导体晶圆(图源:三星电子)

抢占3nm先发优势,或已有客户导入

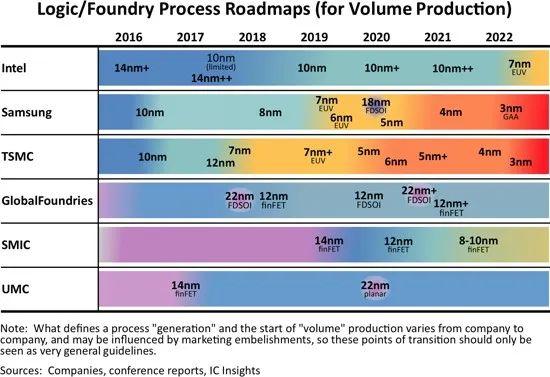

超越台积电、成为全球代工市场龙头,是三星一直以来的目标。在先进制程的演进过程中,台积电始终领先三星一步,抢占更多市场资源。

为了赶超台积电,三星不断加大资本支出,2021年三星芯片业务资本支出超过360亿美元,超越台积电同年度的投资规模。而在先进制程的研发方面,三星的战略布局也略显激进。

早在2019年,三星便将3nm工艺节点纳入其半导体路线图中,并计划于2021年提供首批样品,2022年正式量产。而在去年7月,在2021年国产IP与定制芯片生产大会上,三星电子公开了下一代芯片代工制程规划,即3nm制程将于2023年投产。

对此,三星回应称,三星3nm工艺节点将分为3GAE和3GAP两个版本,前者将于2022年如期量产,后者将于2023年大规模量产。

图源:IC Insights

今年早些时候,三星被曝出“良率造假”,正深入调查资金流向及产量报告等问题,重点关注5nm至3nm良率。受此影响,三星晶圆代工的主要客户正在流失,高通、英伟达等客户纷纷转单台积电。

在7nm与5nm节点上的落后,让三星对3nm工艺制程寄予厚望。此次,三星率先宣布3nm生产计划,一定程度上抢占了3nm芯片市场先发优势,这也是三星超越台积电的一次重大押注。

据韩媒TheElec 28日报道,三星电子3nm工艺将于本周开始试生产,中国比特币挖矿芯片公司PanSemi(上海磐矽半导体)或为首批客户,也有消息称高通也已预定3nm工艺芯片代工订单。

3nm之争,GAAFET还是FinFET?

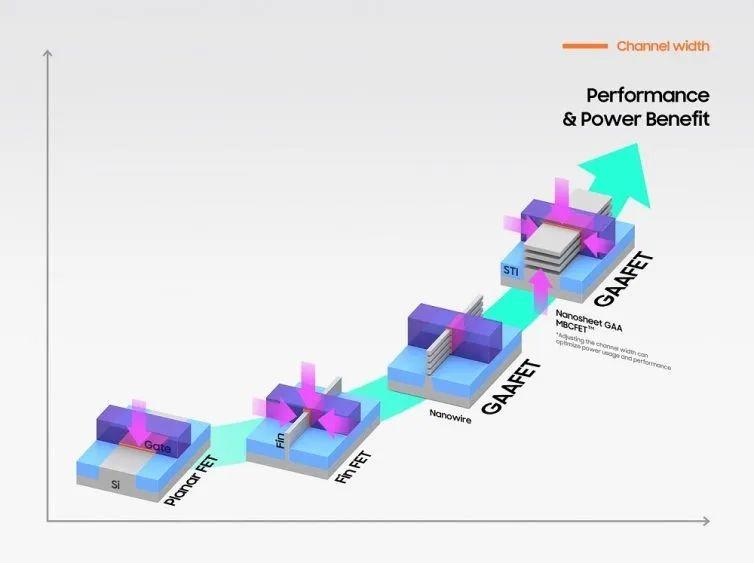

回到工艺制程本身,三星自3nm节点开始放弃了FinFET工艺,率先转向了GAA晶体管工艺。而从各家公布的路线来看,台积电在3nm工艺制程上仍然基于FinFET工艺,预计到2nm工艺节点才开始转向GAA工艺,而英特尔则计划在Intel 20A工艺改用GAA晶体管(英特尔称RibbonFET晶体管)。

与传统FinFET相比,GAAFET采用纳米线沟道设计,栅极可以完全包裹沟道外轮廓,因而对沟道控制性更好。GAAFET晶体管拥有更好的静电特性,且能以更低的功耗实现更好的开关效果。

根据源极与漏极间通道的长宽比不同,GAAFET晶体管又分为纳米线结构和纳米片结构。三星3nm工艺采用了后一种多层堆叠纳米片的GAA结构,并将其定义为MBCFET。

三星晶体管结构路线图(图源:三星电子)

三星3nm MBCFET技术在设计上具有高度灵活性,可调整纳米晶体管的通道宽度,从而优化功耗和性能,满足客户多元需求。GAA技术的这种设计灵活性有助于设计技术协同优化,提高芯片功耗、性能、面积(PPA)优势。

同时,三星也提及3nm设计基础设施与服务的重要性。为此,自2021年第三季度以来,三星电子协同ANSYS、楷登电子、西门子和新思科技等SAFE(三星先进晶圆代工生态系统)合作伙伴,共同打造更稳定的设计环境,帮助客户减少设计、验证和批准过程所需时间,提供产品可靠性。

先进制程竞争白热化

随着先进工艺节点不断演进,芯片的性能、功耗及成本越来越难以平衡,芯片制造难度也翻倍增长。在三星3nm工艺制程宣布生产之后,芯片制造领域市场的竞争将趋于白热化。预计台积电与英特尔将会加速先进制程的研发工作,进一步加大投资与产能建设,以抢夺市场领先优势。

在2nm工艺制程方面,台积电与三星也你争我赶,不肯落后一步。6月中旬,据台积电披露,到2024年,台积电将导入ASML高数值孔径极紫外光刻机,用于生产GAAFET架构的2nm芯片,预计2025年开始量产。而Business Korea报告显示,三星也将于2025年大规模生产基于GAA的2nm芯片。

在3nm工艺制程上,三星以先发优势暂且领先台积电。显然,三星本次的官宣也将为其提振市场信心,弥补此前因良率问题造成的客户信任危机。然而,三星真正实现超越台积电,还要看其3nm芯片实际的良率、性能及功耗水平。