FPGA教学——如何将易灵思FPGA干到750MHz(1080P显示)

2022-08-29

作者:电子技术应用专栏作家 疯狂的FPGA

来源:电子技术应用专栏作家 疯狂的FPGA

前阵子写过一篇文章《如何才能半导体雪崩中活下来》,然后昨天任老爷子就发布了讲话,即接下来是全球经济衰退期,为了保证度过未来三年的“经济”危机,缩减业务,核心聚焦,不再关注销售额,而是现金流/利润为王。

为了活下来,我们可以躺平;我们需要卧薪尝胆,既然不适合去轰轰烈烈赶一把,我们反而可以利用这段时间,卧薪尝胆,好好学习。前阵子出差+工作耽搁了下,内心无比愧疚,今天重新开始学习分享FPGA知识,欢迎各位斧正。

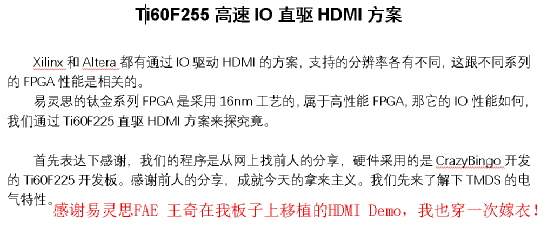

拿来主义的好处就是,相对效率会更高一点,并且试错成本还低很多。那么在此感谢原厂FAE王奇抢先一步在我的开发板商移植HDMI,让我们在易灵思Ti60 FPGA上一睹为快。

易灵思钛金系列FPGA Ti60F255的开发板,出炉已经有一些日子了,板载HDMI电路理论上是成熟的(别家FPGA上我验证过),但却一直没能挤出时间来移植一下HDMI 1.4的显示方案,今天我们就来挑战一下IO模拟1080P60,把易灵思Ti60 FPGA干到750MHz主频!

这部分采用FPGA模拟的话,电路其实非常简单,加了EMC芯片后的原理图如下所示。

HDMI 采用和 DVI 相同的传输原理——TMDS最小化传输差分信号。TMDS 传输系统分为两个部分:发送端和接收端。TMDS 发送端收到HDMI 接口传来的24bit RGB信号,然后对这些数据进行编码和并/串转换,再将RGB 信号的数据分别分配到独立的传输通道发送出去。接收端接收来自发送端的串行信号,对其进行解码和串/并转换,然后发送到显示器的控制端;与此同时也接收时钟信号,以实现同步。

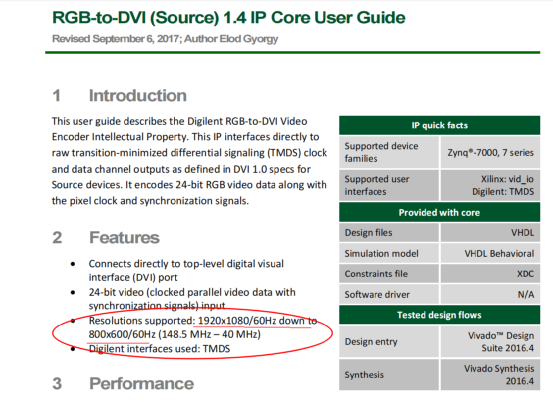

网上很多FPGA模拟HDMI PHY的设计,可参见https://zhuanlan.zhihu.com/p/435937460。其中以Digilent的HDMI IP最为常见,其采用VHDL模拟TMDS,用FPGA实现HDMI的收发,节省了外部PHY芯片的成本(https://github.com/Digilent/vivado-library)。

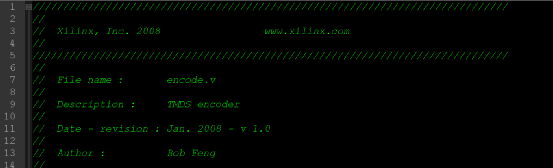

Digilent HDMI IP方案,后来很多朋友其他平台上都有移植,我也在Xilinx和安路上都有移植测到过,其采用VHDL实现,稍微有点复杂。不过今天我将在FAE王奇的基础上,消化吸收另一个HDMI tx ip(采用Verilog编写,结构很简单),在易灵思Ti60 FPGA挑战下1080P60(其实主频主要还是看收发器的速率)。这里也感谢这个HDMI IP创作者的劳动果实,Verilog Header如下:

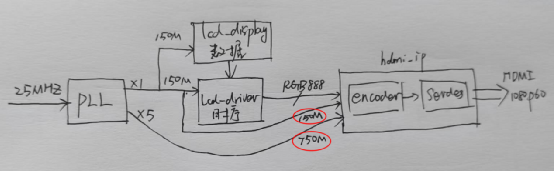

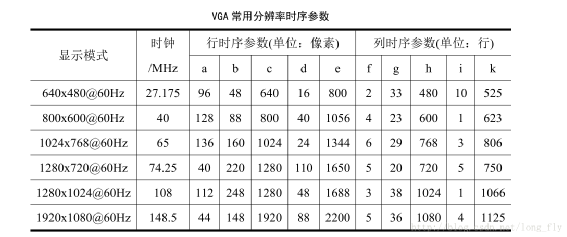

给出目前的框图,如下所示,外部输入25M,由Interface的PLL生成150/750MHz(离开148.5MHz有点偏差也没关系),hdmi_ip接收前面测试的RGB数据后,模拟HDMI协议发送给外部,在显示器上显示。由于TMDS用10bit编码,FPGA采用DDR模式进行数据发送,因此当串行时钟是像素时钟的10/2=5倍。

我们在Interface中配置PLL,这里输入25M,输出150+750MHz,如下图所示:

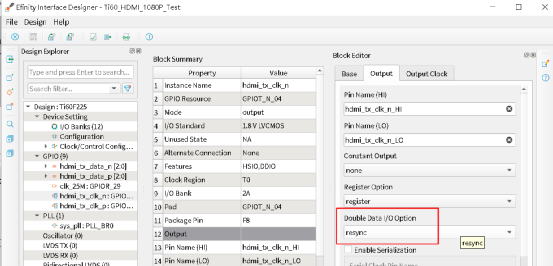

另外,这里的关键是我们采用易灵思的Double Data IO,配置如下,这里将hdmi_tx_data和hdmi_tx_clk都打开了resync模式:

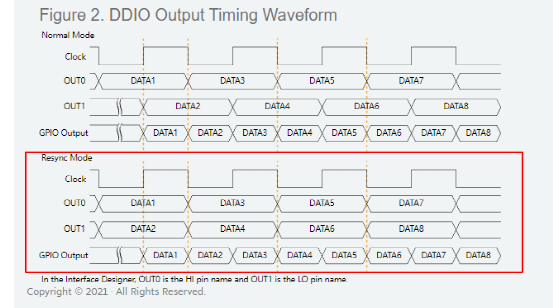

查询Efinity help文档,可以看到DDIO的Resync Mode,用户在Clock下降沿输入OUT0+OUT1,GPIO在上升沿输出OUT0,在Clock下降沿输出OUT1,从而达到了倍频的目的(这里的HI就是OUT0,LO就是OUT1)。

那么在代码中,我们需要驱动GPIO DDIO前的HI与LO,我们的顶层代码如下:

这部分通过serdes_4b_10to1.v文件编码输出,相关代码如下所示:

最后,采用Efinity进行综合,上图中的逻辑跑到了750MHz,DDIO实现了1.5Gbps的带宽。DDIO 1.5Gbps已经是易灵思的瓶颈了,虽然时序有一点小违例(150M到750M跨时钟域部分电路),但是HDMI 1080P60已经成功显示,如下所示(盗用8年前的图,懒得拍)。

本来打算移植LVDS模式,但是频率上不去,目前怀疑HDMI电路还得加上拉电阻,当前版本省略了,以后有机会再试试。下一步,上T35移植HDMI测试一下能跑到多少频率,至少应该能跑720P吧?

本文配套开发板Ti60F225 FPGA开发板,请转crazyfpga.taobao.com(CB电子铺)了解更多。

对易灵思FPGA感兴趣的朋友,欢迎进FPGA微信群交流,我们共同进步,等待疫情过去,我们重新坐起来。

由于群规模在短时间内超过了200人,无法再扫码入群,请有兴趣的朋友添加客服同学的微信,再邀请入群。

关于FPGA国产替代,以及FPGA解决方案咨询,欢迎加入知识星球一对一探讨交流,碰撞思维火花。

更多信息可以来这里获取==>>电子技术应用-AET<<

电子技术应用专栏作家: 疯狂的FPGA