伟大的工程之芯片制造

2022-09-20

来源:温戈

纵观整个制造业,芯片的制造流程可以说是最复杂的之一,这项点石成金术可分为八个大步骤,如下图所示,这些步骤又可细分为上百道工序。

制造硅晶圆

制造硅晶圆的原料是我们最常见的沙子,沙子的主要成分是二氧化硅,将沙子进行提纯得到单质硅,然后再通过直拉法得到单晶硅锭,先将硅锭两端切去,再切成几段,进行滚磨,目的是使单晶硅棒达到标准直径。接下来采用X射线法确定单晶硅的晶向,切除参考面,再以参考面为基准进行切割得到硅晶圆,如下图所示。

得到初步的晶圆后,要将切好的硅晶圆进行倒角、研磨处理,让其表面变得平整光滑,否则难以在上面刻制正确的电路。研磨过后还要用化学腐蚀液去除研磨过程中的损伤,最后用抛光液进行抛光,经检验合格后,即可交给产线进行制造了。

薄膜沉积

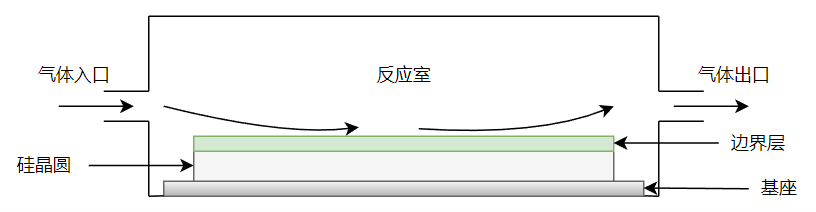

第二步到第六步是需要多次重复的过程。薄膜沉积(deposition)是将材料薄膜沉积到晶圆表面上,沉积材料可能是导体、半导体和绝缘体,常见的薄膜有二氧化硅薄膜、多晶硅薄膜、氮化硅薄膜、金属及化合物薄膜等。常用的沉积方法有化学气相沉积(Chemical Vapor Deposition,CVD) 和物理气相沉积(Physical Vapor Deposition,PVD)。CVD是把构成薄膜物质的气态反应剂或液态反应剂的蒸汽以合理的流速引入反应室,在衬底表面发生化学反应,沉积成膜的工艺方法,如下图所示。

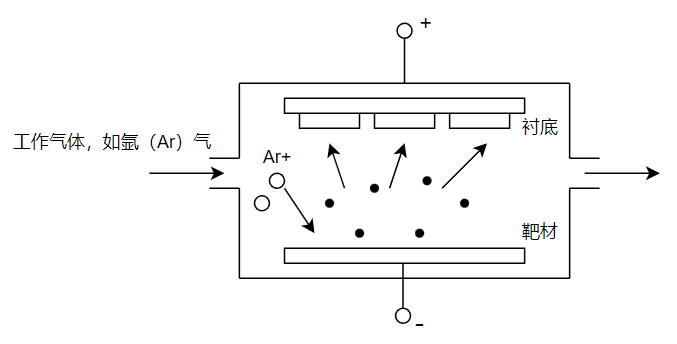

物理气相沉积是指在真空条件下,采用物理方法,将材料源(固体或液体)气化成气态原子或分子,或部分电离成离子,转移到硅衬底表面形成薄膜的过程,如图3-5所示。PVD相比CVD而言,优点是工艺原理简单、工艺所需温度低,能用于制备各种薄膜。缺点是台阶覆盖(step-coverage)性、附着性、致密性不如CVD薄膜。

PVD的常见种类包括溅射镀膜、真空蒸镀、等离子体镀膜等。以溅射镀膜为例,是指在一定真空度下,使气体等离子化,其中的离子轰击靶材表面,靶材表面的原子等粒子气相转移到达衬底,在衬底表面沉积成膜的过程,如下图所示。

光刻

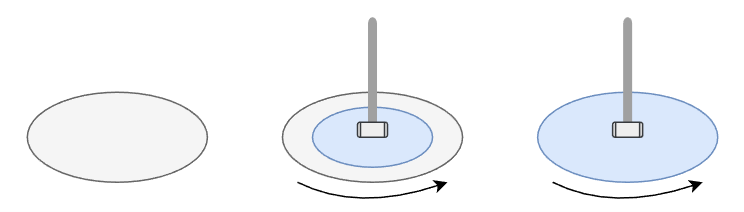

光刻是整个制造中最核心的一步。光刻前要在晶圆上均匀的涂上光刻胶(photoresist),通常光刻胶采用旋涂的方式,即边旋转,边涂抹,保证光刻胶的均匀性,如下图所示。

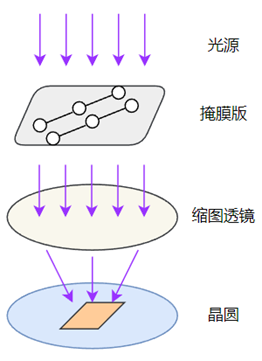

将涂光刻胶后的晶圆放入光刻机中,光刻机的光源发出的深紫外(DUV)或极紫外(EUV)光透过掩模版(也称作光罩),将掩膜版上的电路结构图案缩小并聚焦到光刻胶图层上,光刻胶在受光后,受光区域会发生化学变化,掩膜版上的电路图形就会印刻到光刻胶图层上,此步骤称为曝光,如下图所示。曝光之后的步骤是烘烤和显影,目的是去除图形未覆盖区域的光刻胶,从而让印刷好的电路图案显现出来,永久固定。

刻蚀

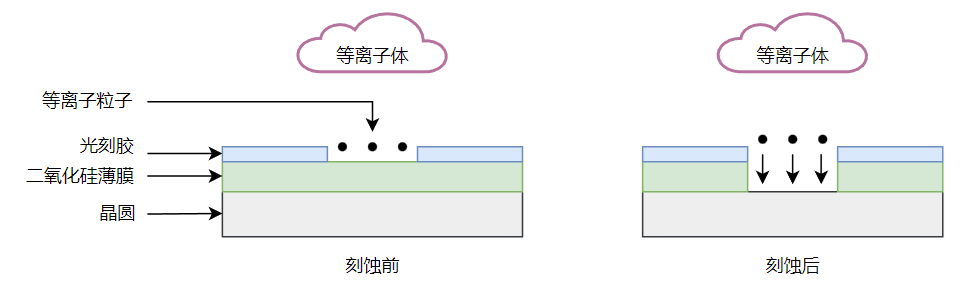

刻蚀(etch)是在光刻步骤完成后,用化学或物理方法有选择地从硅片表面去除不需要的材料,从而只留下3D电路图的过程。刻蚀方法主要包括湿法刻蚀(wet etching)和干法刻蚀(dry etching),湿法刻蚀是指利用化学溶液与预刻蚀材料之间的化学反应来去除未被掩蔽膜材料掩蔽的部分而达到刻蚀目的。干法刻蚀是用等离子体化学活性较强的性质进薄膜刻蚀的技术,干法刻蚀又包括溅射刻蚀(Supptter Etching)、等离子体刻蚀(Plasma Etching)、反应离子刻蚀(Reactive Ion Etching,RIE)。刻蚀过程以等离子体刻蚀为例,利用等离子体中的粒子,撞击二氧化硅薄膜层,达到去除多余氧化层的目的,如下图所示。

计量和检测

刻蚀结束后要对晶圆计量和检测,确保没有误差。如果检测结果不符合预期,则应反馈至光刻或者刻蚀步骤,做进一步的优化及调整。事实上,计量和检测可以贯穿整个制造流程。

离子注入

离子注入就是将要掺杂的原子(如Ⅲ、Ⅴ族元素),在强电场的作用下,被加速射入到晶圆的特定区域,再进行退火、激活杂质、修复晶格损伤等步骤,从而获得所需的杂质浓度,最终形成N区或者P区。

互联

互连就是讲同一芯片内各个独立的元器件,通过一定的方式,连接成具有一定功能的电路模块的技术。用于互连工艺的金属材料需具备低电阻率、热化学稳定性好、抗电迁移特性佳、易于沉积和刻蚀、价格低廉等特征。集成电路发展早期主要使用铝互连工艺,但因为铜具有比铝更低的电阻率,和更好的抗电迁移特定,而被广泛采用。

从薄膜沉积到互连这六个步骤,在整个制造流程中会重复几十次甚至上百次,每一次重复,都会在晶圆上刻制一层电路,最终形成完整的芯片。以上所有步骤完成后,对晶圆整体进行打磨、抛光等,再进行测试及封装,合格的芯片就可以出厂交付了!

更多信息可以来这里获取==>>电子技术应用-AET<<