教学:如何测试FPGA的供电电源

2022-09-25

来源:Comtech FPGA

在硬件设计电路中,根据芯片功能复杂度,可编程芯片一般都需要不止一种供电电源来驱动芯片内部的不同功能块,而FPGA具备逻辑可编程、编程灵活度更高、高集成度等特点,供电电源种类繁多,需要硬件设计人员格外关注。

以AMD-Xilinx FPGA为例,不同的制程工艺下针对用户的各种需求,会规划有多个产品系列,其中集成不同功能、不同性能的功能模块,因此我们按照功能模块划分来描述AMD-Xilinx FPGA需要的各种供电电源,简单把电源种类分为PL供电电源、PS供电电源、集成功能块供电电源。

每个系列FPGA产品的供电电源种类、名称、电压值、精度要求、去耦电容要求会有差异,具体设计时请工程师参照对应芯片系列的手册详细查询,本文中不对供电电源种类、名称、电压值、精度要求、去耦电容要求等做详细解释。

PL供电电源:VCCO、VCCAUX、VCCAUX_IO、VCCINT、VCCINT_IO、VCCBRAM、VBATT、VCCADC等。

PS供电电源:VCC_PSINTFP、VCC_PSINTLP、VCC_PSAUX、VCC_PSINTFP_DDR、VCC_PSPLL、VPS_MGTRAVCC、VPS_MGTRAVTT、VCCO_PSDDR、VCC_PSDDR_PLL、VCCO_PSIO、VCC_PSBATT等。

集成功能块供电电源:

A. VCU供电电源:VCCINT_VCU;

B. XADC/System Monitor供电电源:VCCADC、VREFP、VREFN等;

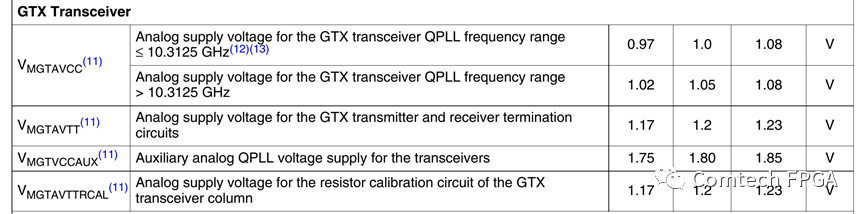

C. GT Transceiver供电电源:VCCINT_GT、VMGTAVCC、VMGTAVTT、VMGTVCCAUX、VMGTAVTTRCAL等;

D. HBM供电电源:VCC_HBM、VCC_IO_HBM、VCCAUX_HBM等;

E. RF供电电源:VADC_AVCC、VADC_AVCCAUX、VDAC_AVCC、VDAC_AVCCAUX、VDAC_AVTT、VCCINT_AMS、VCCSDFEC等;

二、如何测试FPGA的供电电源

硬件工程师通常会在硬件设计初期对各路电源的功耗做预估并留有设计裕量,此时强烈推荐硬件设计工程师、逻辑设计工程师和嵌入式软件设计工程师一起参与,使用XPE工具和已有的设计工程来进行功耗预估;在硬件焊接完毕之后硬件设计工程师也会测试各路电源的电压值、纹波等参数指标,都确认OK后才会交给逻辑设计工程师去做外设、接口的测试。

针对支持客户过程中遇到的几个典型问题,作者根据自己的理解给出电源测试的几点建议,欢迎硬件设计工程师们邮件来交流讨论:

A. 测试电压值时不建议使用万用表,建议使用示波器的平均值功能,并调节合适的档位;

B. 硬件设计中通常为了方便断开电源,会在电源输出进FPGA之前添加磁珠或者电感,磁珠和电感会引入压降,建议在磁珠和电感之后测试;如无磁珠和电感,建议测试点尽量靠近FPGA的电源PIN;

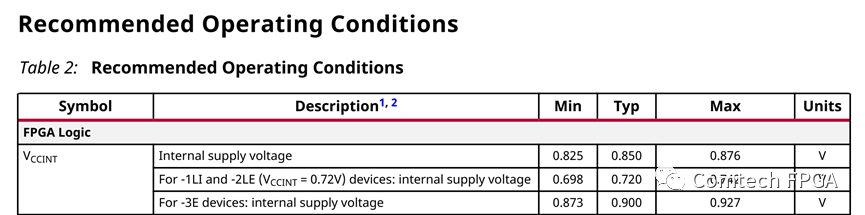

C. 每个系列的FPGA都有对应的DC and AC SwTIching CharacterisTIcs手册,里面会给出每种电源的电压值要求范围,实测电源电压值在考虑上纹波的影响后不要超出手册要求范围,尽量不要接近下限;举例说明:Kintex Ultrascale+器件的VCCINT电压值在DS922上要求如下图,若我们使用0.85V供电,在测试电压值时,考虑上纹波的影响,不要超出0.825V~0.876V的范围,也尽量不要接近0.825V的下限电压;

D. 纹波测试时选择合适的档位、使用交流耦合、打开20MHz带宽抑制;

E. 带负载测试,FPGA加载程序和不加载程序时,功耗差异大,对于电源输出电压和纹波特性有影响,所以在测试电源时尽量使用完整的设计程序测试;在逻辑和软件调试的后期也不要因为板卡刚焊接好时硬件工程师测试过电源,而不敢怀疑电源问题;

三、电源影响FPGA功能和性能的几个典型案例

电源影响功能和性能的几个典型案例:

案例A:电源影响GT Transceiver性能

用户使用K7 FPGA做HDMI2.0 TX设计,输出4K@60fps视频点屏,屏幕上有噪点,测试客户板卡上GTX相关的MGTAVCC、MGTAVTT、MGTVCCAUX电源,发现MGTAVTT的纹波40+mV。

用户在二次改板时修改了电源去耦电容,优化了纹波,但是改板后在测试HDMI TX点屏时,4K@30fps点屏测试OK,4K@60fps点屏不成功。

使用IBERT测试,IBERT 6Gbps Near-end PCS环回测试OK,IBERT Near-end PMA环回测试链路不稳定,会间歇性no link;而Ibert 3Gbps Near-end PCS环回和Near-end PMA环回均OK。

怀疑到MGTAVTT电源,经过测试发现,MGTAVTT在FPGA未加载程序时电压值测试正常、纹波在30mV以内;MGTAVTT在FPGA加载程序后电源电压从1.198V跌落到了1.18V,考虑上纹波影响后,可能会超出1.17V的下限,调高MGTAVTT电源电压值后,4K@60fps点屏测试工作正常。

案例B:电源影响GT Transceiver性能

用户使用V5器件做XAUI设计,在实验室环境下测试所有功能正常,最终用户的板卡插到机房的标准机柜中测试时发现有数据丢帧现象,测试MGTAVCC、MGTAVTT、MGTVCCAUX电源的电压值和纹波,均符合手册要求的范围。

经过和用户一起分析,认为机房中电磁干扰可能比较大,最终把MGTAVTT调整到比标准值1.20V略大,提升Transceiver PMA抗干扰能力,问题解决。

案例C:电源影响Memory初始化完成

用户使用A7 FPGA,外接DDR3 Memory,在样机研制阶段没有发现问题,进入批产阶段后,在生产的几千块板卡中有几百块不能正常工作,通过JTAG调试发现DDR3的init_calib_complete为0,初始化无法完成。

换用MIG的example design测试,发现在有故障的板卡上使用example design也无法初始化完成,通常在MIG example design测试不过的时候我们考虑电源、时钟、PCB的影响,由于客户批量生产中大部分板卡整个程序测试OK,因此我们排除掉PCB的影响。

在测试电源时,我们发现用户硬件设计时在接DDR3的BANK VCCO供电的1.5V实测值为1.48V,经过一个磁珠后电压值为1.46V,考虑上纹波的影响,到达FPGA VCCO PIN的电压可能低至1.44V,我们拆掉磁珠直接短接两个焊点后,DDR3 example design测试OK,用户的完整应用测试也OK。

案例D:电源影响VCU工作

用户使用ZU4EV来做视频编解码设计,编码端使用VCU做4路1080P视频的压缩,测试中发现当使能2路1080P视频压缩时编码板工作正常,当使用软件命令启动第3路视频的压缩时,VCU编码功能挂死;而解码板只做2路1080P视频的解压缩,所以解码板的VCU未发现问题。

我们在软件侧尝试做工作,检查VCU的IP配置,尝试在VCU编码挂死时重新加载VCU的驱动,使用不同的Vivado版本、Petalinux版本、驱动版本等,测试现象一致。

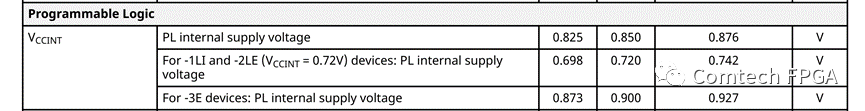

检查用户的原理图,发现VCCINT_VCU和VCC_INT是同一路电源供电,前端电源芯片输出0.85V电压,查证后得知,早期的Xilinx手册上写VCCINT_VCU可以0.85V供电,在现在的手册上VCCINT_VCU要求0.9V供电。

![]()

测试中发现,VCCINT经过一个磁珠后给VCCINT_VCU,在VCU启动到编码功能时,磁珠的压降变化,每启动一路1080P视频编码,整板功耗增加约1W;在启动到第3路1080P编码时,磁珠的压降大至0.03V,VCCINT_VCU跌落至0.82V,VCU不能正常工作。

最终我们去掉磁珠,把VCCINT和VCCINT_VCU的电压调高至0.87V,用户完整设计工作正常。

更多信息可以来这里获取==>>电子技术应用-AET<<