先进封装,扮演重要角色!

2023-02-09

作者: Yole

来源: 半导体行业观察

随着半导体前端节点变得越来越小,设计成本快速增加。在这种情况下,先进封装及其 2.5D 和 3D 解决方案在降低与前端制造相关的成本影响方面变得至关重要且有效,同时还有助于提高系统性能并提供更低的延迟、更高的带宽和电源效率。

根据 Yole 的定义,如果一个die能在每平方毫米内能集成超过16个pitch小于130μm的I/O。如超高密度 (UHD) 扇出、嵌入式硅桥、硅中介层、3D 堆栈存储器(例如 3D NAND)、高带宽存储器(HBM)和 3D 堆栈 DRAM 就是满足这些标准的一些封装平台(图1)。

另一个值得考虑的平台是 3DSoC,它采用芯片到晶圆 (D2W:die-to-wafer) 的混合键合。嵌入式硅桥(embedded Si bridges)有两种可能的选择:第一种,称为 EMIB,由 Intel 提出并嵌入IC基板中;第二种是嵌入模制化合物(mold compound)中的硅中介层,由 TSMC (LSI) 和 SPIL (FOEB) 提供。

具体到硅中介层( Si interposers)方面,则有两种产品:一种是传统的或非有源的,通常由 TSMC、三星和 UMC 提供;另一种是有源的,即英特尔的 Foveros。把EMIB 与 Foveros 结合则产生了 Co-EMIB,这个技术被应用到了英特尔的 Ponte Vecchio处理器上。三星、SK海力士和美光则提供了3D 堆叠 DRAM 和 HBM 内存。

值得一提的是,长江存储是迄今唯一一家使用晶圆对晶圆(W2W:wafer to wafer) 混合键合技术生产 3D NAND 的公司。但包括铠侠和上述三家公司在哪的竞争对手都在考虑进攻这项技术。

此外,Sony(自2015年起)和OmniVision(自2022年起)这样的CIS供应商使用W2W混合键合生产的CMOS图像传感器也是一种3D堆叠封装平台,但它们不是高端性能平台,因为它不能满足I/O方面密度和间距的要求 ,这代表着其与上述封装有着相当的差距。

前途无量的先进封装市场

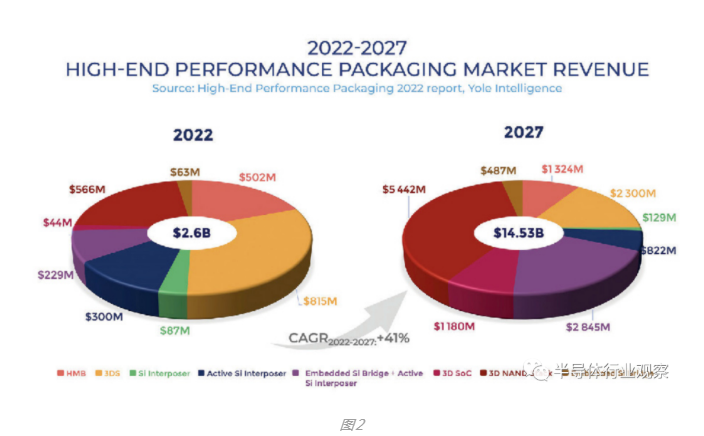

与其他封装平台相比,高端性能封装的单位数量很小,但由于其复杂性导致平均售价较高,因此它产生的收入比例更高。预计到 2027 年收入将超过145亿美元,高于 2022 年的 26亿美元,这就意味着其在2022到2027年间的CAGR为41%(图 2)。

这种健康增长归因于包括云计算、网络、人工智能、自动驾驶、个人计算和游戏在内的高性能计算终端系统的增加。这些应用都需要用更复杂的节点生产更大、更复杂的芯片,这些节点会随着成本的增加而扩展。这些趋势促使半导体行业制定具有高端封装选项的系统级扩展策略,而不仅仅是扩展 FE 高级节点。

通过将大型单片 SoC 裸片拆分成更小的芯片并仅缩放最关键的电路组件,小芯片以及异构集成是降低缩放成本的一种选择。这只能通过使用具有高连接密度、高带宽和良好功率效率的 2.5D 和 3D 集成技术来实现。因此,由于研发和生产方面的重大进步,微凸块、硅通孔 (TSV)、铜柱和混合键合正在推动高端性能应用中的 IO 密度和功能集成达到新高度。

3D SoC(包括die-to-wafer和die-to-die混合封装)则被看作是10μm以下pitch技术的下一个突破点。作为前端封装技术,这使得高端系统级性能与3D DRAM的更密集的3D IC堆叠、异构集成封装和封装分区SoC die成为可能。领先的供应商,尤其是台积电、三星和英特尔,都以此为目标,提供或计划提供尖端的混合键合解决方案。这也许是半导体和封装世界之间的真正接触点。

先进封装正在向前端靠拢。证据在于代工厂和 IDM,因为它们正在成为市场上最先进的2.5D 和 3D 封装解决方案领导者。OSAT 正努力顺应这一趋势,提供创新的先进封装解决方案,以帮助解决摩尔定律放缓带来的前端挑战,但他们要打入混合键合市场将是极其困难的,因为他们缺乏前端能力和必要的资源。

当然,我们也必须承认,没有事情是百分百的。

拆解当前的先进封装市场

封装技术不断发展,以满足日益增长的芯片集成度和对每个组件更高性能的需求。芯片封装已经完成了从其传统用途的演变。在传统用途中,芯片封装仅用作芯片保护。现在,封装的设计选择在解决缩放的减速和满足对高性能的多样化需求方面起着至关重要的作用。

通过2.5D&3D异构封装技术也实现了更小的占用空间和超高布线。

最近,新的参与者进入了先进封装解决方案领域,以提高其高端产品的性能。各种架构和功能也用于增强die之间的互连。例如,硅通孔与die之间的垂直连接已成为一种有吸引力的解决方案,可用于减小封装尺寸、提高信号完整性并在 HBM 存储器中提供更高的数据传输速率。传统的铜微凸块用于创建短而快速的芯片到芯片或芯片到基板的互连。尽管缩小凸点(bumps)变得越来越困难,但一些厂商已经推出了一种使用混合键合的新解决方案,以提供直接的、更高密度的互连和可扩展的互连间距。

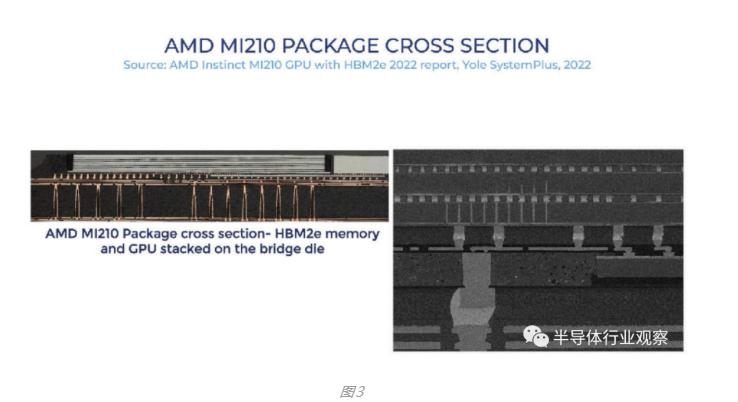

Yole 对先进封装市场最近出现的各种封装解决方案进行了分析和比较并发现:NVIDIA 的 A100 使用 TSMC 的大型硅中介层连接 GPU 和 HBM 内存,从而优化了占用空间并提高了组件性能;然而,中介层的成本相对较高,因为封装中超过 50% 的芯片全部对应的中介层芯片。面对这些挑战和硅中介层工艺的成本影响,一些制造商(如 AMD)使用替代解决方案(例如模制中介层 (mold interposer))来减小硅芯片的尺寸和成本。AMD 的 MI210 组件将芯片集成在扇出高架桥接( fan-out elevated bridge technology)技术中,其中多个桥接芯片将处理器裸片连接到 HBM 内存(图 3)。桥接芯片嵌入封装成型中,HBM 和 GPU 裸片堆叠在模具中介层( mold interposer)上,铜柱结构穿过成型件,用于将信号从裸片垂直传输到基板。该解决方案提供了更好的电气性能并降低了成本。

Apple 凭借其 Apple M1 Ultra 组件也进入了先进封装市场,该组件使用本地硅中介层连接两个处理器,将这项技术标记为超融合(ultra-fusion)。这种新颖的封装工艺,包括芯片优先工艺(chip-first)和最后再分配(redistribution last)工艺,这也正是台积电的 InFO-L 工艺。该组件中使用的 LPDDR5 内存并未直接与处理器芯片互连,而是仅集成在封装基板级别。

面对先进封装缩放和互连方面的不同挑战,混合键合已被引入作为各种半导体组件的封装解决方案。

2022年,AMD还首创了V-Cache技术。它通过使用芯片到晶圆混合键合将缓存芯片连接到处理器来使用额外的缓存。这种使能技术允许高速缓存的垂直堆叠,以改进互连、减少键合间距并加快处理器内核对高速缓存的访问。一旦混合键合良率得到优化,该工艺将为 3D 封装提供更有前途的解决方案。

台积电在覆盖前端和后端方面发挥着至关重要的作用,因为它具有制造用于最新处理器芯片的先进节点的代工能力,并提供 OSAT 无法提供的先进和复杂的后端服务。异构解决方案使具有不同功能的多个小芯片和来自不同制造工艺流程的芯片能够集成到一个封装中。主要目标是提供一种具有成本效益的集成方案,同时具有改进的性能、更高的传输速度和更低的功耗。

对设备和材料的要求

先进封装设备与现有平台一样多种多样,服务于所有级别的互连,即在 Si 芯片(或小芯片)、Si 光子芯片、布线或再分布层 (RDL:redistribution layers) 级别。当中还包括如嵌入式桥接器或有机中介层、Si 中介层、IC 基板和高级印刷电路板 (PCB)在内的嵌入式布线。在每个级别,我们都看到了减小互连间距和线间距 (L/S:line space) 的趋势。制造这种互连的复杂性来自于形成它们的各种互连形状和材料。互连类型、制造方法和使用的设备可以根据基板类型(晶圆或面板)和材料(Si、有机、玻璃)进行区分。

晶圆级封装 (WLP) 设备相对完善。该设备不断优化,以应对清洁和温度控制、高纵横比特性、增加的粗糙度、翘曲控制以及对封装中各种材料的考虑等挑战。

硅芯片顶部的布线以及硅通孔 (TSV) 均采用薄膜技术制造。对于宽松的 L/S,可以使用成熟的 MEMS 类型的设备,满足core-FO、扇入、倒装芯片和低端硅中介层的制造需求。对于更严格的 L/S,来自领先设备制造商的前端 300 毫米设备用于制造 BEOL 布线、TSV 或用于高端硅中介层、硅桥接芯片、3D 堆栈存储器和 3D SoC。WLP FO(HD 和 UHD)考虑了略有不同的方法,其中 RDL 或通模通孔(TMV:Through-Mold-Vias)被制造到环氧模塑料 (EMC:Epoxy Mold Compound)。

布线完成后,芯片通过混合键合较大的焊料凸块( bigger solder bumps)、较小的铜柱( smaller Cu pillars)、微凸块(microbumps)或最小的直接铜焊盘(smallest direct Cu pad进行互连。其中,混合键合是设备和材料供应商在芯片和晶圆处理、键合后光刻、沉积、减薄和平面化、蚀刻和等离子切割以及混合互连核心方面的技术转折点。

面板级封装 (PLP) 设备和材料供应链更为复杂,通常使用定制设备在 EMC、有机面板、味之素积层膜(ABF)和玻璃之上互连。PLP 可以使用减材( subtractive)或增材(additive)工艺,其中设备优化通常受到表面贴装技术 (SMT)、半导体和平板显示器行业的启发,以解决非对称翘曲、更厚的基板、涂层或沉积的均匀性和减薄、粗糙度增加以及处理低温材料等挑战。此外,由于缺乏适用于严格 L/S 的面板处理计量和检测工具,PLP 过程控制很困难。IC 基板和先进的 PCB 面临互连间距减小的挑战,我们看到从 SMT 到薄膜的转变技术。对于嵌入式桥接器的拾取和放置以及层压到有机面板中的互连间距变得更加严格,RDL-first 用于 2.3D 有机中介层或 Chip-last FO。

总而言之,WLP 和 PLP 技术的改进与高端硅芯片的进步是互补的。因此,我们继续看到许多令人振奋的发展。

欢迎关注电子技术应用2023年2月22日==>>商业航天研讨会<<