捷联惯性导航计算机系统架构发展综述

2023-02-22

来源:电子产品世界

本文引用地址:http://www.eepw.com.cn/article/202302/443565.htm

0 引言

惯性导航系统(Inertial Navigation System,INS)[1],是利用陀螺仪和加速度计[2],测量载体的加速度和角速度,并实时解算其速度、位置及姿态的系统[3]。惯性导航系统在运行过程中既不会接收外部信号,更不会向外辐射电磁波。高隐蔽性、全天候、快速响应[4]的特性使得惯导系统在飞机、舰船、火箭和战略武器中起到了核心的作用。同时惯性导航也在逐步走向民用,在海底勘探、地下开发、隧道施工、机器人技术等新的国民经济应用场景下,有着大量的工业落地案例,发挥了巨大作用[5]。

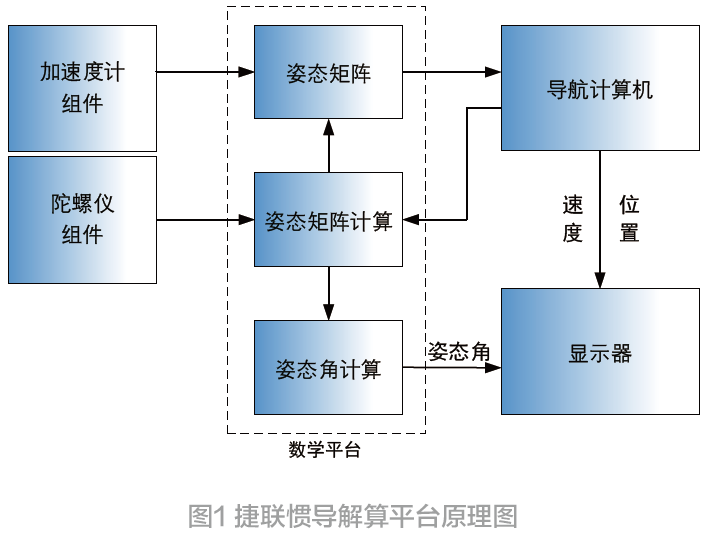

惯性导航系统根据原理不同包含平台和捷联两类。前者将惯性敏感器件安装在机械平台上,建立惯性坐标系;而后者则将其直接安装于载体本身,建立导航坐标系。前者的结构一般较复杂,体积庞大,低灵活性大大限制了应用场景,后者利用数学计算平台取代了传统的机械结构物理平台,大大简化了系统结构。体积小、成本低、便于安装、灵活更新的诸多优点使得捷联惯导系统脱颖而出,在21 世纪后广泛取代了平台惯导系统。

第二次世界大战时期,德国人VonBraun 率先设计出了V-2 型火箭,它的成功发射揭开了“惯性导航技术”这一新兴的领域。1970 年4 月,美国宇航局的“阿波罗13 号”载人飞船在任务过程中发生严重爆炸后,凭借备用的捷联导航系统,得以安全返回地面,至此惯性导航技术的发展迈上了新的台阶并愈发成熟[6]。国内的惯性技术依赖苏联进行艰难起步,筚路蓝缕。在进入2000年后,以我国的“神舟”飞船为首的航天事业广泛应用了捷联惯导技术,在战略武器和运载火箭等国防领域成为了中坚力量。本文将重点聚焦于捷联惯导系统的核心计算机架构及其硬件平台,通过分析捷联惯导计算机的不同架构、系统组成,对其硬件架构的发展迭代情况进行总结归纳,并结合时下的新技术对其未来发展方向提出预测。

1 导航计算机的任务分析

不管导航计算机安装在何种类型的物体上,它的基本工作内容都可以总结提炼出3 个基本方面:采集、解算、通信。

1.1 数据采集

通过特定串口采集陀螺仪和加速度计的输出数据[7]。由于输出的信号类型会含有模拟信号,所以要设计信号的A/D 转换,把模拟信号转换成为可以被处理的数字信号,这个过程中往往还伴有调理滤波等。部分场景还要考虑到温度对惯性敏感元件的影响,进行温度信号的采样处理。

1.2 数据解算

数据解算的实质就是利用上个时刻的导航信息,计算出这个时刻的导航信息,包括姿态、速度、位置[8]。

1.3 和PC通信

前两步产生的数据要传输给PC 机,进行输入数据和导航数据的存储。同时需要考虑到程序错误、内存溢出等常见故障的报警和检测功能[9]。

2 导航计算机发展现状

导航计算机诞生之初,直接采用的是体积和重量都十分庞大,且运行功耗很高的PC 机,但由于其过于得不够灵活已经被淘汰[10]。之后人们开始考虑研制专用的平台来完成这一特定的任务。1980 年前后,研究人员开始使用PC/104 导航计算机,它通过单独开发主板及插卡的架构,大幅度削减了体积和功耗。同时为了提高适用性采用了更为通用的电源供电。其处理器通用配置是Intel公司的 8086,运行在Linux 和DOS 操作系统下。但是PC/104 要扩展多串行口和外接AD 采样卡,进而降低了其灵活性,使其几乎无法应用在较小型运载体上,因此降低功耗和缩减体积的目标还是迫在眉睫[11]。

随着半导体和电子产业的革命性发展,通用CPU、微控制器MCU 和DSP 处理器的优势逐步展露[12]。伴随嵌入式编程的兴起,科研机构开始研究使用各种嵌入式处理器作为核心的导航计算机。本文将聚焦国内科研单位和高校对导航计算机的研究,通过梳理大量的文献,针对常见的导航计算机的体系结构进行了分类总结,并指出不同体系结构的优势和不足。

2.1 以DSP、ARM或单片机作为单独的核心处理器

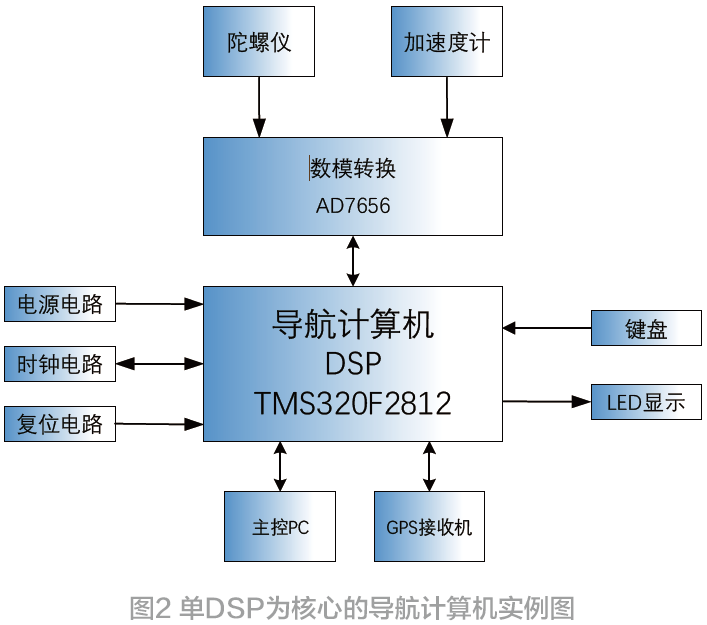

电子科技大学的纪杭辛选用了32 位TI 公司的DSP芯片TMS320F2812 作核心[13],负责主要的导航解算任务。同时为了克服随时间积累的误差,外挂了GPS 接收机构成组合导航,进一步成功实现了GPS/INS 位置和速度组合解算。

以浮点DSP 为核心的优势是精度高,对采集到的数据,解算处理速率快,但其缺点是需要扩展接口来克服外设接口比较少的弊端,但是外接扩展反而会增大导航计算机的体积与功耗[14]。纵然ARM 拥有更完善的软件生态系统,在接口控制和数据传输方面胜过DSP,但是解算速度慢于高性能的DSP。因此单核心的导航计算机大多选择DSP。

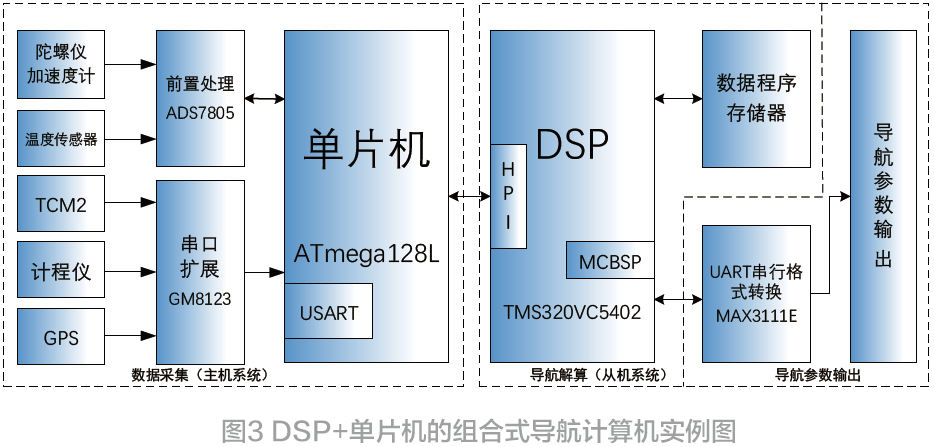

2.2 DSP 或ARM与单片机的双机组合系统

哈尔滨工程大学的金红新使用单片机ATmega128L和DSP TMS320VC5402 进行组合设计了导航计算机[15]。拥有丰富的外设接口的单片机作为主机,负责数据采集任务,预处理任务和系统控制任务,DSP 则担任从机的角色,专注于导航解算等任务,绕开了自身较为薄弱的数据交换和外设控制。这种“主机+ 从机”的主从式、紧藕合的导航计算机的优势明显成为主流选择。

双机组合的主从结构系统面临的一大困难,便是双芯之间的数据交换和共享。对数据的实时性要求很高,采集的导航数据和DSP 每次接收到的数据都要确保是最新的。在整个软件的设计流程中,如何避免单片机和DSP 在同一时间,对同一数据存储区进行同时操作而产生读写冲突成了必须要重视的问题。因此双机主从结构的导航计算机的通信编程常常十分复杂,从而降低整个系统可靠性、稳定性,提升了开发设计难度。

2.3 DSP和ARM组合

为了攻克双处理器主从结构在数据交换上的难题,DSP+ARM 的思路也应运而生。高性能、低功耗的ARM控制接口丰富,数据采集和系统控制的能力强悍,十分适合和DSP 组合设计捷联导航计算机,便于控制体积和功耗,保证性能等同时不失适用性[16]。但弊端在于系统硬件结构基本固定后,扩展性受到大大的限制。特别是后续如果计划针对系统的功能进行附加和软硬件升级,则十分不方便。因此,这种结构的惯导计算机并没有大规模应用到实际工程和设计任务当中。

2.4 DSP和FPGA的组合

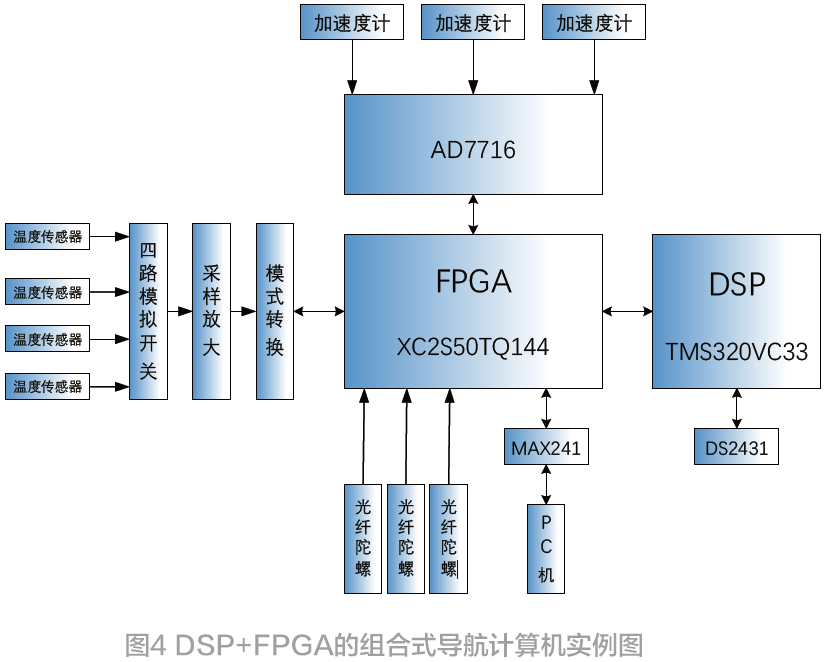

进入21 世纪人们希望将导航计算机部署应用在更多的场景中。这种需求对导航计算机进一步提出了体积更小、成本更低、维护更方便等新发展方向和要求[17]。特别是半导体芯片革命性的迭代发展使得迷你捷联导航系统成为了可能。FPGA 拥有丰富的逻辑资源、强大的逻辑控制和时序控制能力,让人们看到了应用的可能。特别是它还有足够的扩展IO 接口,并且在数字信号处理方面的不俗能力,使得利用FPGA 设计捷联导航计算机成为现实。

哈尔滨工程大学的杨枭以“DSP+FPGA”作为双核心的硬件架构,设计了基于光纤陀螺的捷联导航数据处理系统[18]。由FPGA 完成数据采集后,用多余的资源代替DSP 进行滤波工作,DSP 只承担接收数据后的解算。由于光纤陀螺零漂、标度因子的性能指标对温度变化十分敏感,必须引入温度采集模块来进行温度补偿。整个系统工作过程中,可以通过引入中断响应来给FPGA滤波时间,完成任务后向DSP 提出中断请求,再由DSP 来读取数据[19]。特别的是,光纤捷联惯导系统数据采集模块含有模拟电路,而惯导核心解算模块为数字电路,应使用光电耦合器,隔离数据采集模块和导航计算机模块,从而提高电路可靠性和性能指标。

DSP 满足导航计算机对解算算法的高精度要求,且FPGA 众多的接口便于实现功能自定义,即使有外接扩展其他设备的需求也能十分灵活地应对。DSP+FPGA这一对组合在保证了高性能、高可靠性的核心要求前提下,也符合了小体积、低功耗的新发展要求。最重要的是,整个系统后期的升级维护方便,确定的硬件不需要升级和改变,只需要对相应的软件算法进行升级迭代就可以设计定制化极强的导航计算机。因此这种结构的导航计算机迅速成为了当下最主流的选择。

2.5 SOC和SOPC结构

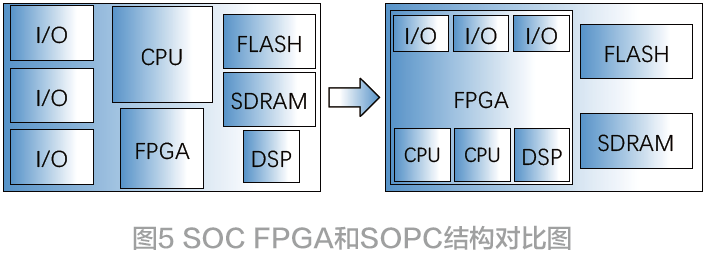

SOC(System On Chip,片上系统)是由中央处理器控制存储器件和其他功能模块并将他们统一集成在一枚芯片上的片上系统。将传统的DSP 或ARM 硬核处理器系统和FPGA 再进行进一步集成,就是SOC FPGA。当前十分成熟产品有Intel 公司的 Cyclone V SOCFPGA。如图所示,它在ARM 和FPGA 之间进行大带宽高速连接,同时拥有两者的优势:既可以灵活地运行图形化Linux,又可灵活定制丰富的IO。SOC FPGA 在导航解算方面有很大的应用空间和前景,可以最大化利用FPGA 的可编程优势,完成导航数据采集和处理,进而辅助协同ARM 进行导航数据的解算。

进一步来说,SOPC(System On a Programmable Chip,可编程片上系统)是一种特殊的SOC FPGA,最大不同在于FPGA 利用集成好的资源实现软核CPU 而非使用硬核CPU[20]。硬核处理器在不使用时仍要占用FPGA 资源,而人为搭建的软核处理器(NIOS II)在不使用时全部的硬件资源可给FPGA 当作资源来使用[21]。SOPC 设计方式是依据目标需求进行增加和删减,极为灵活。它的软件和硬件都可在系统级上进行定制化编程,是目前导航计算机研究的一大热点[22]。

3 结束语

通过梳理分析不同的惯导计算机系统架构可以看出,捷联导航计算机的架构和硬件方案在过去的20 年间始终在变化、更新,其重要的现实原因就是半导体技术不断进步所诞生的更为优秀的核心处理器在不断变化。这里对捷联惯性导航计算机未来的发展方向做出进一步的展望和预测:

1)进一步实现更低成本、更小体积和更低功耗仍然是迫切的发展愿景;

2)充分利用半导体电子设计行业的自动化设计技术,进一步进行硬件系统可编程的开发,设计出以SOCFPGA 和SOPC 架构为代表的扩展性更强、自定义程度更高的定制化导航计算机系统;

3)针对嵌入式操作系统更广泛的挖掘和迭代,通过软件设计提升系统核心算法的可靠性。

参考文献:

[1] 陈哲.捷联惯导系统原理[M].北京:宇航出版社,1986.

[2] 惠欣.基于虚拟仪器技术的捷联惯性导航系统仿真研究[D].哈尔滨:哈尔滨工程大学,2008.

[3] 徐锐.船用光纤陀螺捷联惯导系统初始对准技术研究[D].哈尔滨:哈尔滨工业大学,2013.

[4] 陆元九.陀螺仪及惯性技术导航原理[M].北京:科学出版社,1964.

[ 5 ] KAZUSUKE M . Cur r e n t MEMS t e c h n o l o g y a n d MEMS sensors focusing on inertial sensors[C]. ICSICT,

Beijing,2008, IEEE:2008:2371-2374.

[6] D.H.TITTERTON, J.L.WESTON. Strap down inertial navigation technology[M]. London United Kingdom, The Institution of Electrical Engineers,1997.

[7] 尹德进.捷联惯导系统六加速度计配置方案研究[J].中国惯性技术学报,2003,11(2):48-51.

[8] 杜海龙.捷联惯导系统姿态解算模块的实现[J].光学精密工程,2008(10):1956-1962.

[9] 高梅国,刘国满,田黎育.高速数字信号处理器结构与系统[M].北京:清华大学出版社,2009.

[10] 李涛,练军想,曹聚亮,等.GNSS与惯性及多传感器组合导航系统原理[J]. 北京:国防工业出版社, 2011(11)78-135.

[11] 张复宜. SINS/GPS组合导航双DSP硬件平台的设计研究[D].哈尔滨:哈尔滨工程大学,2012.

[12] 彭启琮,李玉柏,管庆. DSP技术的发展与应用[M].北京:高等教育出版社,2007.

[13] 纪杭辛.基于DSP的某型卫星导航计算机信息处理系统设计[D].成都:电子科技大学,2013.

[14] 李莎.捷联惯性导航计算机小型化设计[J].导航与控制,2014(4):11-16.

[15] 金红新.基于DSP的导航计算机研究[D].哈尔滨:哈尔滨工程大学,2006.

[16] 孙光民.SINS/GPS组合导航系统设计与DSP实现[J].微计算机信息,2008(31):227-229.

[17] 汪振国.捷联导航计算机的数据采集系统设计[D].哈尔滨:哈尔滨工程大学,2013.

[18] 杨枭.光纤陀螺捷联导航数据处理系统软硬件设计与实现[D].哈尔滨:哈尔滨工程大学,2007.

[19] Texas Incorporated.TMS320C6000 系列 DSP 的 CPU与外设[M].北京:清华大学出版社,2007.

[20] 罗阳.微惯性组合导航芯片体系结构及其关键技术研究[D].长沙:国防科技大学,2009.

[21] 李耀,崔燕.基于 Nios II 的导航系统平台的设计[J].微计算机信息, 2006(32)2-3.

[22] LONG Da-feng.FPGA在组合导航系统中的应用研究[J].机械工程与自动化,2008(4):126-128.

(本文来源于《电子产品世界》杂志2023年2月期)

更多信息可以来这里获取==>>电子技术应用-AET<<