半导体产业,未来十年路线图

2023-10-25

作者: 李飞

来源:半导体行业观察

半导体行业的发展离不开行业的共识,而行业的共识往往体现在行业所公认的路线图里面。在上世纪末,美国的半导体工业协会SIA联合欧洲和亚洲的半导体行业,开始发布大名鼎鼎的国际半导体技术路线图(ITRS)。ITRS主要的贡献是通过协调全球的半导体行业,发布了在21世纪初十多年中的芯片技术路线图,包括特征尺寸,功率密度,逻辑门密度等等。到了2015年,随着传统基于2D CMOS特征尺寸缩小的摩尔定律的发展到了尾声,ITRS也不再更新,因此2015年版本就是ITRS的最后一个版本。在当时,作为ITRS的牵头方之一,SIA发表声明将会在未来合适的时候发布新的半导体路线图。而在上周,SIA和SRC联合发布了微电子和高级封装路线图,作为ITRS的后继者。

MAPT路线图主要针对未来十年左右(2023-2035)的时间范围,首先分析了时间范围内对于芯片行业的应用需求,包括主要驱动应用、能效比需求以及安全需求,并且根据这些需求,分别分析了半导体各细分行业(数字处理、高级封装和异构继承、模拟和混合信号半导体、硅光技术和MEMS、半导体工艺、设计建模和测试标准、半导体材料以及供应链)需要所对应的技术进步来满足这些需求。

首先,MAPT路线图分析了未来十年内预期对于半导体行业最重要的驱动应用,其中最重要的包括:

数据中心和高性能计算

汽车电子

物联网和边缘计算

移动通信

生物计算

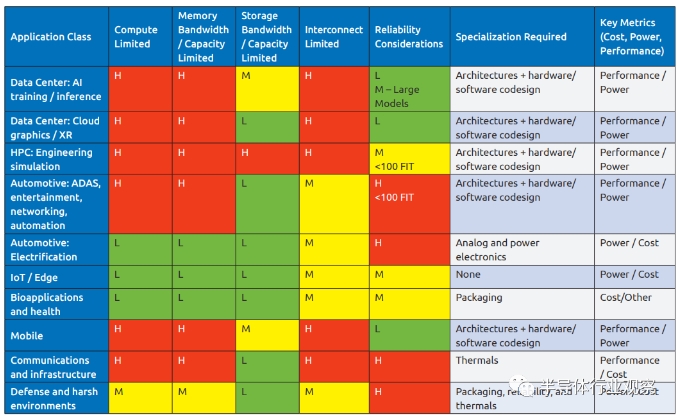

在MAPT路线图中,分别列出了不同的驱动应用主要的瓶颈、需要的专门技术以及最关键的指标。从分析中,我们可以看到,计算和存储瓶颈将会成为未来驱动应用中最关键的瓶颈,另外互联带宽也在几个重要的驱动应用中成为瓶颈;而在核心指标方面,最关键的指标基本都指向了性能和功耗。因此,从驱动应用的角度,未来十多年间半导体芯片行业进步的方向也就很明确了:通过进一步提升计算、内存和数据互联性能以满足几大重要驱动应用的需求,同时通过优化设计来实现对于功耗的要求。由于性能和功耗同时都很重要,能效比这一指标可望会成为未来十年间半导体芯片领域最关键的指标——事实上,在MAPT路线图中,“能效比”这个词就被重复了接近120次,可见其重要程度。

数字芯片:逻辑密度增速减慢,架构创新驱动技术进步

数字芯片向来是半导体芯片中最核心的品类,其出货量大,对于半导体芯片工艺的依赖度高,往往是驱动整个半导体行业发展的核心芯片品类;因此在在MAPT路线图中,对于数字芯片相关的路线图分析也是最详实的。

在关于数字芯片的路线图中,我们首先看到了和以往摩尔定律所预测的截然不同的数字。MAPT路线图预计,未来十年,晶体管密度将从目前的200亿每平方厘米增加到800亿每平方厘米,即10年增加4倍。在过去,摩尔定律预测每18个月晶体管密度翻倍,因此10年间晶体管密度应该增加64倍以上,这样来看根据MAPT的路线图预测,未来晶体管密度的增长速度会远远低于之前摩尔定律的速度——未来十年的晶体管密度上升速度,仅仅相当于过去三年的水平。

而如果我们仔细看最近几年的半导体工艺演进的话,我们可以发现事实上晶体管性能(即门延迟)的改善甚至更落后于之前摩尔定律所预测的每18个月提升40% - 目前来看每代工艺演进在集成度翻倍的同时,晶体管性能仅仅提升10-20%之间,而在未来这个数字甚至会更小。因此,从MAPT路线图中,我们可以大概估算出,未来十年中,随着晶体管集成度翻四倍,晶体管的性能提升大约在20-30%左右。换句话说,数字芯片性能提升基本不能依靠晶体管性能提升,而是要依靠其他的方法。

在MAPT中,数字逻辑未来的进步主要靠架构上的进步。MAPT提出主要的进步方向包括:

进一步提升集成度:由于半导体工艺进步在未来十年中对于逻辑密度的提升贡献有限,为了进一步提升集成度,主要需要依靠高级封装技术。高级封装技术可以用不同的堆叠方式(2.5D以及3D)把不同的芯片粒(chiplet)集成在同一个封装里并且可以解决先进工艺的良率问题,因此可望在未来中高端芯片中得到更广泛的应用。

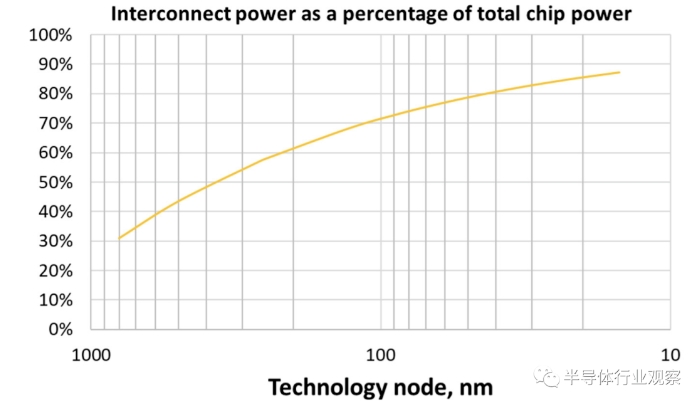

降低数据移动开销:随着未来芯片集成度越来愈高(即逻辑越来越复杂),数据互联的开销将会成为芯片性能和能效比的主要瓶颈;例如,根据之前的研究,在10nm节点,高复杂度的SoC中数据互联的功耗开销已经占到整个芯片功耗的90%左右,而未来随着复杂度和集成度进一步提升,数据互联将会越来越成为瓶颈。为了解决这个问题,一方面需要使用高级封装技术——例如,通过3D堆叠,互联的物理距离会大大降低(因为可以垂直走线),从而降低功耗;另一个重点则是通过新的架构,例如近内存计算和存内计算,来降低开销;最后,模拟和混合信号电路的创新也能降低数据移动的开销。

使用更多的专用设计架构(domain-specific design)来取代通用设计——例如使用AI加速器来进行人工智能相关的计算(而不是使用通用架构例如CPU和常规GPU),这样做可以大大改善能效比。当使用专用设计的架构时,软硬件协同设计就将成为一个核心概念,因为在设计专用架构时,需要考虑软件和应用层的实际需求(例如对于AI加速器来说,就是专用数制和特定算符的支持),从而实现高效率。另外,使用专用架构时,可以使用芯片粒技术,把不同的架构使用多个芯片粒实现,并且使用高级封装技术集成在一起。

从以上分析可以看出,MAPT对于数字逻辑电路的进一步演进是以高级封装技术为主线,使用基于高级封装技术进一步提升集成度、降低数据移动开销并且实现专用架构设计的集成,从而让芯片性能和能效比在未来十年中继续摩尔定律时代的指数级提升。

高级封装技术:技术快速演进成为行业支柱

正如MAPT在数字逻辑章节的分析,高级封装将成为未来半导体的主旋律。

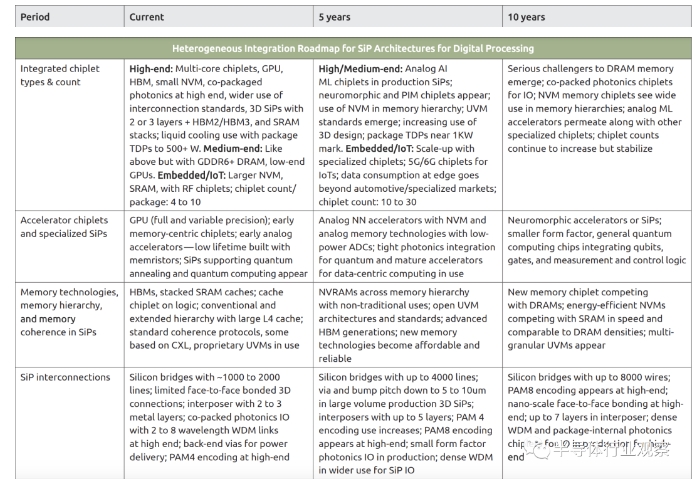

例如,在未来五年中,一个系统中芯片粒的数量将从今天的4-10提升到10-30(提升3倍),预计在十年的时间内芯片粒数量会提升更多;在内存角度,芯片粒将会实现新的内存架构,从而改善内存墙问题,到时候希望内存的容量、速度和功耗将不再成为整个系统的瓶颈;在互联方面,未来10年高级封装的互联线数量将从今天的1000-2000上升到8000,另外使用新的IO接口技术(例如PAM8,以及高密度WDM光学互联)来进一步提升数据带宽并降低数据移动开销。

这些需求具体对应到高级封装的技术演进,MAPT在高级封装章节提出了未来十年的技术演进方向。

我们认为,在高级封装未来十年中,最关键的技术演进包括:

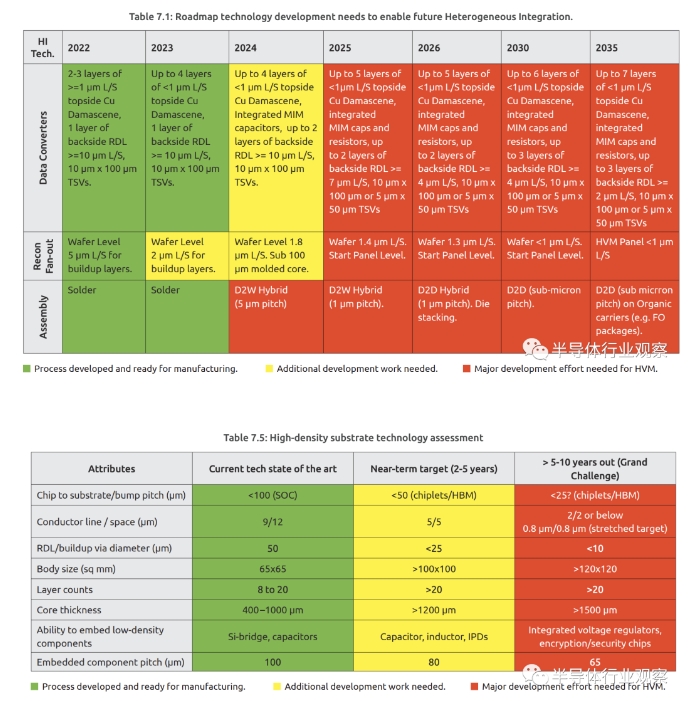

进一步提升IO密度:将芯片粒之间的bump(焊球)间距从100微米降低到25微米,从而将IO密度提升16倍。

进一步提升IO互联线密度:这里的互联线密度包括在晶圆正面将今天的2-3层线间距大于1微米的顶层铜互联发展到7层线间距小于1微米的铜互联,晶圆背面的RDL层互联从一层上升到三层互联并且将线间距从10微米降低到2微米;以及在晶圆间的互联线间距从5微米降低到1微米,即互联线密度提升25倍。

革新集成键合技术:从目前基于焊接(solder)的键合集成技术逐渐改进到die-to-wafer以及die-to-die的键合。新的集成键合技术将是实现高密度IO的核心技术。

从高级封装技术的演进路线图,我们可以看到摩尔定律的指数规律正在高级封装领域继续发生。在未来十年中,高级封装的IO密度将预计会提升16倍,IO互联密度提升25倍,这大约是每2.2-2.5年翻倍的规律,这和之前摩尔定律预计每1.5年芯片晶体管密度翻倍的规律相近,只是翻倍时间从1.5年变成了2.5年。

模拟和混合信号:无线通信和功率电子的核心

模拟和混合信号电路在未来十年的半导体路线图中也扮演了重要角色,因为模拟和混合信号电路仍将是重要应用的赋能技术。

模拟和混合信号电路的第一个核心应用是无线通信。预计在未来10年,无线通信对于数据率的需求仍将持续上升,而为了支持更高的数据率,需要在更高的载波频率使用更高的带宽,同时需要电路的性能(线性度、噪声系数等)持续演进。

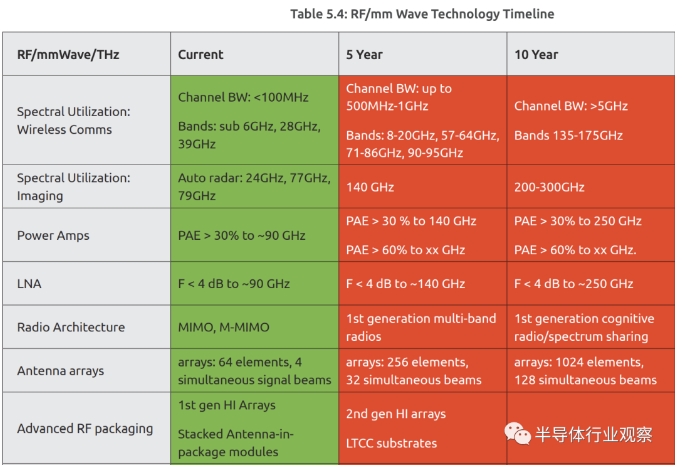

具体到无线通信模拟混合信号电路路线图中,我们可以看到一些核心的指标演进:

载波频率从今天的低于40GHz演进到175GHz,同时带宽从今天的100MHz上升到5GHz

低噪声放大器系数保持在4 dB附近,但是工作频率从最高支持90GHz上升到250 GHz

功率放大器的效率保持30%,但是支持的频率从90GHz上升到250GHz

天线阵列的复杂度大大提升,从目前的64单元提升到1024单元

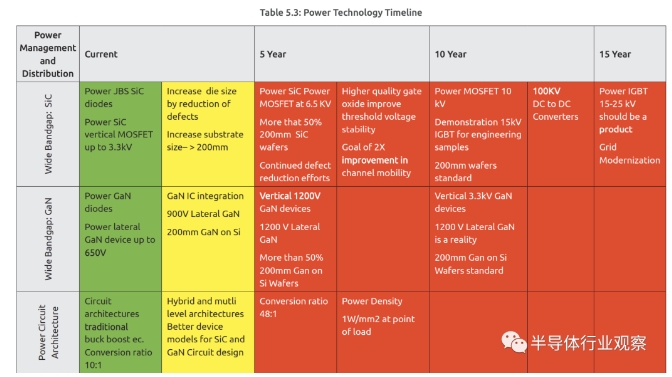

除了无线通信之外,另一个模拟和混合信号的赋能领域是功率电子。未来十年,功率电子应用预计越来越多:人工智能的进一步普及需要更多数据中心,而数据中心需要高效率供电模块以确保总体能效比;新能源汽车更进一步得到使用,需要更高效率的功率芯片;太阳能等新能源变得越来越主流,也需要功率电子的配合。

在路线图中,我们可以看到GaN和SiC功率电子芯片都会得到长足的发展。对于SiC来说,预计未来10-15年,支持的电压将从今天的3.3kV拓展到15-25kV,从而为新能源应用提供支持,同时也进一步增加器件载流子移动速率以提升器件的性能(支持更高的开关频率);而GaN也在提供高器件性能和开关频率的同时增加对于高电压的支持,从今天的650V提升到3.3kV,而除此之外另一个重要的演进方向是进一步提升GaN对于硅基底(GaN on Silicon)的支持,在10年后预计200mm GaN-on-silicon晶圆将成为标准配置,从而进一步降低GaN的成本并且有机会支持更方便的高级封装集成。