三星16层及以上HBM需采用混合键合技术

內存堆叠高度受限

2024-06-12

来源:芯智讯

6月11日消息,据韩国媒体Thelec报道,三星上个月在2024年IEEE上发表的一篇题为《用于HBM堆叠的D2W(芯粒到芯片)铜键合技术研究》的论文,提到16层及以上的高带宽內存(HBM)必须采用混合键合技术(Hybrid bonding)。

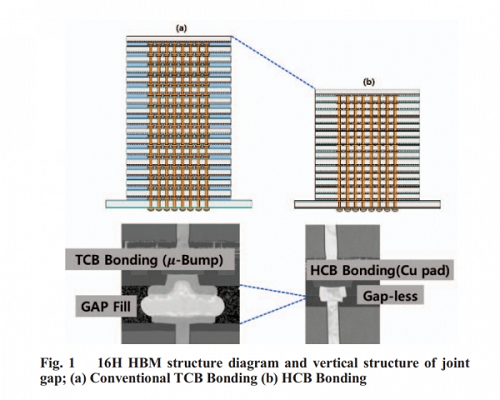

据了解,混合键合是下一代封装技术,目的是芯片透过硅穿孔(TSV)或微型铜线进行垂直堆叠时,中间没有凸点。韩媒The Elec指出,由于是直接堆叠,所以混合键合也称为“直接键合”。

与目前三星所使用的热压焊接(TC)相比,Hybrid bonding可焊接更多芯片堆叠,维持更低的堆叠高度并提高热排放效率。三星指出,降低高度是采用混合键合的主因,內存高度限制在775微米内,在这高度中须封装17个芯片(即一个基底芯片和16个核心芯片),因此缩小芯片间的间隙,是內存大厂必须克服的问题。

最开始DRAM大厂计划尽可能减少核心芯片的厚度,或者减少凸点间距,但除混合键合外,这两种方法都已达极限。知情人士透露,很难将核心芯片做得比30微米更薄。由于凸点具有体积,通过凸块连接芯片会有一定局限性。

三星4月使用子公司Semes的混合键合设备制作了16层的HBM样品,并表示芯片运作正常。目前贝思半导体(BESI)和韩华精密机械(Hanwha Precision Machinery)也在开发混合键合设备。传闻三星计划在2025年制造出16层堆叠的HBM4样品,并于2026年量产。

本站内容除特别声明的原创文章之外,转载内容只为传递更多信息,并不代表本网站赞同其观点。转载的所有的文章、图片、音/视频文件等资料的版权归版权所有权人所有。本站采用的非本站原创文章及图片等内容无法一一联系确认版权者。如涉及作品内容、版权和其它问题,请及时通过电子邮件或电话通知我们,以便迅速采取适当措施,避免给双方造成不必要的经济损失。联系电话:010-82306118;邮箱:aet@chinaaet.com。