Intel Arrow Lake P/E大小核布局变了

有两大好处

2024-07-02

来源:快科技

7月2日消息,Intel 12/13/14代酷睿都是P/E混合架构设计,俗称大小核,整体布局是一致的,但是下一代的Arrow Lake,也就是酷睿Ultra 200系列(没有15代酷睿了),将会迎来一次变革。

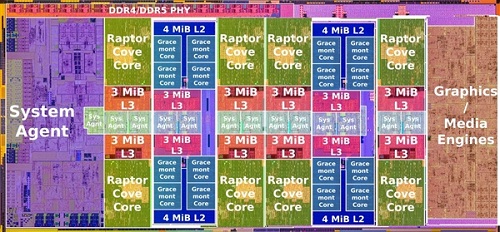

在目前的架构中,P核、E核、GPU核显、I/O控制器等亿次都挂靠在一条环形总线(Ring Bug),其中P核是一个整体(最多8个),E核是另一个整体(最多16个)。

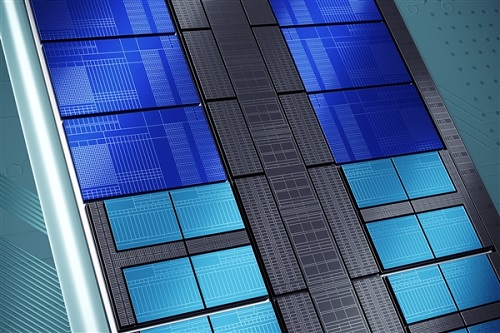

Arrow Lake(包括低功耗版Lunar Lake)的具体架构图现在是没有的,但是有高手根据已知信息做了一个示意图如下:

P核、E核不再是独立的两部分,而是混合在一起,每一个P核的旁边是四个E核组成的集群,各有自己对应的三级缓存。

环形总线通信的时候,先经过一个P核,然后是四个E核,接下来是两个P核,再往后是四个核,紧接着一个P核,如此往复。

这么做的好处看起来有两个,一是P核、E核之间的通信延迟会大大缩小,可以直接互通,而不需要间隔好几站。

比如当线程调度器需要分配不同负载给不同的P核、E核的时候,或者某个负载需要在P核、E核之间转移的时候,效率会高得多。

二是改善散热,更加均衡。

比如在游戏等高负载场景中,不会再集中使用P核而导致这部分区域集中发热,E核部分则基本闲置。

当然,具体的Arrow Lake架构设计,还需要等发布之后再挖掘更具体的信息。

本站内容除特别声明的原创文章之外,转载内容只为传递更多信息,并不代表本网站赞同其观点。转载的所有的文章、图片、音/视频文件等资料的版权归版权所有权人所有。本站采用的非本站原创文章及图片等内容无法一一联系确认版权者。如涉及作品内容、版权和其它问题,请及时通过电子邮件或电话通知我们,以便迅速采取适当措施,避免给双方造成不必要的经济损失。联系电话:010-82306118;邮箱:aet@chinaaet.com。