全球第二台High NA EUV光刻机即将进入英特尔奥勒冈州晶圆厂

2024-08-07

来源:芯智讯

8月6日消息,在近日的英特尔财报电话会议上,英特尔CEO帕特·基辛格(Pat Gelsinger)透露,全球第二台High NA (高数值孔径)EUV光刻机即将进入英特尔位于美国奥勒冈州的晶圆厂。

ASML此前在二季度财报会议上也表示,该公司已经开始向客户出货其第二台High NA EUV光刻机,但是并未指出是哪家客户。现在来看,这家客户正是英特尔。

资料显示,ASML的第一代High NA EUV(EXE:5000)的分辨率为 8nm,可以实现比现有EUV光刻机小1.7倍物理特征的微缩,从将单次曝光的晶体管密度提高2.9倍,可以使芯片制造商能够简化其制造流程。并且,EXE:5000每小时可光刻超过 185 个晶圆,与已在大批量制造中使用的 NXE 系统相比还有所增加。ASML还制定了到 2025 年推出的第二代High NA EUV光刻机将产能提高到每小时 220 片晶圆的路线图,确保将High NA EUV光刻机集成到芯片工厂对于芯片制造商来说在经济性上至关重要。根据此前的爆料显示,High NA EUV的售价高达3.5亿欧元一台。

众所周知,英特尔与ASML合作了数十年时间,推动了光刻技术从 193nm浸没式光刻技术发展到 EUV,但出于成本考虑,英特尔选择不在其 10nm 工艺(相当于台积电6nm)中使用该技术。相反,英特尔选择使用标准深紫外 (DUV) 光刻机进行四重图案化,需要对单个芯片层进行四次 DUV 曝光,而不是使用 EUV 进行单次曝光。结果,英特尔在良率方面遇到了重重困难,导致其10nm工艺推迟了五年。这也使得英特尔被台积电、三星等率先使用EUV光刻机的厂商持续超越。

因此,在英特尔CEO基辛格提出“IDM 2.0”战略后,英特尔便迅速重新聚焦于尖端制程工艺的提升,提出的了四年五个工艺节点的计划,希望在2025年凭借Intel 18A实现对于台积电2nm工艺的超越。与此同时,英特尔还希望通过率先采用High NA EUV光刻机来实现对于台积电等竞争对手的持续领先。最终在2030年前实现英特尔代工业务实现收支平衡的运营利润率,并成为全球第二大晶圆代工厂。

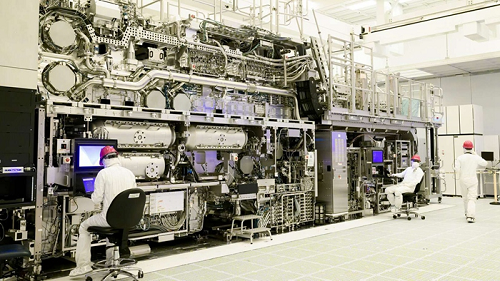

为此,英特尔在2023年12月已率先拿下了全球首台High NA EUV光刻机,并开始在英特尔俄勒冈州晶圆厂安装。一套High NA EUV光刻系统的大小等同于一台双层巴士,重量更高达150吨,相当于两架空中客车A320客机,全套系统需要43 个货运集装箱内的 250个货箱来装运,装机时间预计需要250名工程人员、历时6个月才能安装完成,不仅价格高昂也相当耗时。

今年4月18日,英特尔公司正式宣布在俄勒冈州希尔斯伯勒的研发基地达成了先进半导体制造领域的一个重要里程碑,完成了业界首个商用High NA EUV光刻机的组装。

根据英特尔的计划,High NA EUV光刻机将会首先会被用到Intel 18A的相关测试,以积累相关经验,最终会被用于Intel 14A的量产。

此前的报道显示,ASML已获得十多台High NA EUV光刻机的订单,客户包括台积电、三星、英特尔、美光及SK海力士。ASML CEO Christophe Fouquet指出,DRAM芯片制造商,可能会在2025或2026年开始使用High NA EUV设备。