一种基带芯片抗温漂时钟控制方法及实现

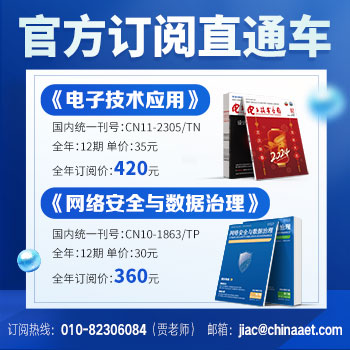

电子技术应用

卢海涛

西安晶汇芯半导体科技有限公司

摘要: 针对多模基带芯片在空闲态下因32 kHz时钟温漂导致网络时基跟踪误差过大的技术难题,提出一种融合高频时钟延长校准、两级PLL级联架构及硬件自动切换机制的时钟控制方案。通过高频校准单元协同时间处理单元(TPU)与睡眠模块(LPM),在空闲态维持高频时钟工作以动态校准32 kHz时钟温漂,并利用两级PLL级联生成高精度基准时钟,结合硬件电路实现高低频时钟的无毛刺切换。

中图分类号:TN402 文献标志码:A DOI: 10.16157/j.issn.0258-7998.256917

中文引用格式: 卢海涛. 一种基带芯片抗温漂时钟控制方法及实现[J]. 电子技术应用,2026,52(2):35-38.

英文引用格式: Lu Haitao. Method and implementation of clock control for baseband chip against temperature drift[J]. Application of Electronic Technique,2026,52(2):35-38.

中文引用格式: 卢海涛. 一种基带芯片抗温漂时钟控制方法及实现[J]. 电子技术应用,2026,52(2):35-38.

英文引用格式: Lu Haitao. Method and implementation of clock control for baseband chip against temperature drift[J]. Application of Electronic Technique,2026,52(2):35-38.

Method and implementation of clock control for baseband chip against temperature drift

Lu Haitao

Xi'an Jinghuixin Semiconductor Technology Co., Ltd.

Abstract: To address the technical challenge of excessive network timebase tracking error caused by 32 kHz clock temperature drift in the idle state of multi-mode baseband chips, this paper proposes a clock control scheme integrating high-frequency clock extended calibration, two-stage PLL cascade architecture, and hardware automatic switching mechanism. The high-frequency calibration unit collaborates with the Time Processing Unit (TPU) and Low Power Mode (LPM) module to maintain the operation of high-frequency clocks in the idle state for dynamic calibration of 32 kHz clock temperature drift. Meanwhile, the two-stage PLL cascade is utilized to generate high-precision reference clocks, and hardware circuits are employed to achieve glitch-free switching between high and low-frequency clocks.

Key words : multi-mode;temperature drift;calibration;protocol stack;paging reception;dynamic switching;network timebase

引言

在现代无线通信终端芯片设计中,时钟系统的稳定性是保障网络同步与数据传输可靠性的核心要素。多模基带芯片在空闲态时,物理层PHY核完成寻呼接收后通常关闭高频时钟,仅依靠32 kHz低频时钟进行网络时基跟踪。然而32 kHz时钟受温度漂移影响显著,其频率抖动较大,导致睡眠期间时基计数偏差不断累积,唤醒后加载的时基值与网络侧同步信息差异过大,终端搜索服务小区成功率过低,用户体验不好。本文通过延长空闲态的高频时钟工作周期,使校准因子(高频时钟与32 kHz比值)更加接近实际情况,这样就能克服温漂并能取得较好的校准效果,不仅能实时搜到小区,而且能降低功耗,用户体验佳,产品有一定竞争力。

主要技术路线如下:

(1)高频时钟延长校准:在空闲态有限延长高频时钟工作周期,利用高频时钟与32 kHz时钟的频率比值动态校准温漂。

(2)两级PLL级联架构:通过第一级PLL生成超稳基准时钟,第二级PLL倍频输出高精度工作时钟,从源头提升时钟基准精度。

(3)硬件自动切换机制:系统发出PLL控制指令后,由硬件电路完成时钟源无缝切换,避免软件干预引入的时序抖动。并通过PLL的LOCK信号和内部硬件计数器的双保护策略,确保PLL输出时钟的稳定性。

本文详细内容请下载:

https://www.chinaaet.com/resource/share/2000006966

作者信息:

卢海涛

(西安晶汇芯半导体科技有限公司,陕西 西安 710065)

此内容为AET网站原创,未经授权禁止转载。