3G LTE(长期演进)是第三代伙伴计划(3GPP)的一个高级标准,为广域网提供下一代宽带无线技术。

与以前各阶段的3GPP相比,3G LTE的目标是更高的吞吐量、更低的时延以及高效的IP回程,提供一种新的可以大规模部署的移动网络技术,预示着一个富媒体和实时服务新时代的到来。

由于最近在HSPA与HSPA+技术上的提升,3G/UMTS必然在未来几年内仍具竞争力,然而,通过3G LTE,3GPP和无线运营商已经在朝着一种更新的、频谱效率(spectral-efficient radio)更高、可扩展、也更加高效的网络架构演进。

最终,3G LTE将使移动运营商能够更有力地与固定宽带服务竞争并继续推动移动对固网的替代。

为实现这些目标,特别设立了3G LTE,以便广泛改善无线和网络通信,同时确保与现有的商业和监管环境的兼容。频率带宽分配就是一个例子,其中,3G LTE必须能够支持与WCDMA同样的频率和频带。但是,尽管WCDMA使用固定的5MHz带宽,3G LTE的设计支持从1.25到20MHz的灵活的载波带宽,以支持即将部署的更精细粒度的频率。

为了进一步改进系统,推出了更多的特性,如用于提高带宽的多天线技术(MIMO:多输入多输出)。利用MIMO技术,在20MHz频段内,峰值数据速率预期将达到下行300Mbps和上行150Mbps。

3G LTE既可被用于成对频谱(FDD)也可被用于非成对频谱(TDD)。对于FDD,上行和下行话务可以在单独的频段内同步传输,而对于TDD,在同一个频带内,上行和下行链路的传输是不连续的。

LTE TDD参数与FDD的参数非常接近,而对于FDD和TDD(滤波除外),LTE L1层也非常类似。

即使不是全部,今天的大多数蜂窝系统使用FDD,而世界上90%以上的可用移动频率都在FDD之内,剩下的10%主要位于最近中国采用的TD-SCDMA内。

3G-LTE的高级技术目标为:下行链路容量:20MHz带宽的瞬时数据速率高达300Mbps;上行链路容量:20MHz带宽的瞬时数据速率可达150Mbps;带宽可扩展至20MHz,覆盖1.25MHz、1.6MHz、5MHz、10MHz、15MHz和20MHz;MIMO支持;FDD及TDD模式;时延:理想条件下,下行链路时延低于0.5ms;用户吞吐量:相当于HSPA+的4.5倍;移动速率:经过优化,支持高达120km/h的速率,但是也支持350km/h的移动速率。

飞思卡尔半导体的MSC8156 DSP

为了满足对高级3G和4G服务的不断增长的需求,无线基础架构设备制造商越来越需要能够提供卓越性能的芯片。通过提供近期基于下一代无线标准,如3G LTE(TDD及FDD)、WiMAX和HSPA+的网络部署所要求的灵活性、集成度和负担能力,飞思卡尔基于StarCore技术的MSC8156 DSP满足了这一需求。尤其是它的出众的性能支持3G LTE基站对高速率、高吞吐量和低时延的要求。

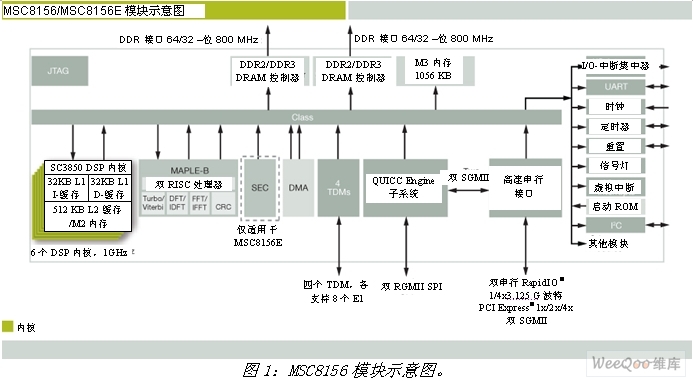

MSC8156是一款基于飞思卡尔先进的SC3850 StarCore DSP内核技术的6核DSP,旨在大幅提升无线基站设备的性能。它提供业界领先的性能和节能水平,在一个高度集成的SoC内,利用45nm处理技术提供与6GHz单核器件等效的性能。MSC8156 DSP把功能集成到以前要求多个独立部件的单一器件内,以此来降低系统成本。

该器件集成了6个完全可编程的SC3850 DSP内核,每个都以1GHz运行,其架构经过高度优化,支持无线基础架构应用。由于采用片上集成,基于MAPLE-B的基带加速器为Turbo和Viterbi通道以及DFT/iDFT和FFT/iFFT算法支持硬件加速。基于内部RISC的QUICC Engine子系统支持多个网络协议,以通过分组网络帮助提供可靠的数据传输,同时从DSP内核大幅分流处理负载。

MSC8156嵌入了大容量内存并支持多种高级的、高速接口类型,包括两个RapidIO互联技术接口、两个用于通信的Gigabit以太网接口、一个PCI Express控制器、两个支持高速、业界标准内存接口的DDR控制器和四个多通道TDM接口。

在开发工具方面,CodeWarrior集成开发环境(IDE)利用Eclipse技术,提供一个高度综合的多核开发环境。它包括:C和C++编译器、源语言调试器、内核和器件模拟器、用于个性化配置和程序/数据跟踪的软件分析插件以及与经过优化的器件驱动器一起提供的免版权费的SmartDSP操作系统。

为了让OEM厂商更快地把产品推向市场,飞思卡尔围绕MSC8156开发了一种综合硬件和软件参考包,其设计目的是为了让系统更快地连接在一起,以便进行*估和开发。开发板和3G LTE参考软件组件详述如下。

MSC8156AMC

基带参考硬件是以MSC8156AMC为基础的,MSC8156AMC后者是一种高密度、单宽全高Advanced MC Advanced Mezzanine Card(AMC) DSP平台,构建于三个MSC8156 DSP基础之上,可插入紧凑型MicroTCA底板。

这种18GHz的处理能力与为无线基础架构应用高度优化的架构相结合,使其成为开发基于下一代无线标准,如(FDD-LTE、TDD-LTE、WiMAX和HSDPA+)的解决方案的理想平台。

每个MSC8156 DSP有1GB的64位宽版DDR3内存,分为两个内存库。对于数据平面应用,高吞吐量的3.125GHz x4 RapidIO链路把三个MSC8156 DSP互相连接起来并将其连接到数据背板。RapidIO接口通过IDT的高带宽10端口(x4)CPS10Q串行RapidIO转换器连接。数据/控制平面应用由1G以太网接口处理。两个1000 Base-X Gigabit接口通过一个以太网转换器把背板连接到DSP。每个DSP有两个通过以太网转换器连接到背板的RGMII接口。在前面板上提供两个额外的Gigabit以太网接口,用于测试和控制。板控制和热插拔由基于Pigeon Point的模块管理控制器提供。

为了有助于未来的开发,围绕“夹层”概念设计了高级夹层卡(AMC)。夹层为系统提供快速实现未来AMC原型系统开发的组成部件。

MSC8156AMC基带L1处理器卡的特性包括:处理器:多达3个MSC8156 6核StarCore DSP,高达1.0GHz的容量,带有集成串行RapidIO以及Gigabit以太网接口;运行:单独或AMC插卡;内存:每个MSC8156具备2 x 512MB的64bit宽版DDR3内存;四个串行RapidIO(sRIO)接口以及两个1000Base-X背板接口;1000Base-T、USB以及UART前面板接口;IPMC:板启动、温度监控、电子键控(E-Keying)以及状态LED指示灯;外形:AMC单宽、全高:180.6mm×73.5mm

L1实时软件子系统

飞思卡尔提供LTE L1支持软件库,包括一个定制操作系统、驱动器和主要信号处理功能。

LTE L1软件包括3GPP标准中定义的物理基带信道处理和无线传输信道功能。飞思卡尔提供一套综合的内核模块,覆盖物理下行链路共享信道和物理上行链路共享信道的L1处理。内核被进一步组合为上行链和下行链,它们以SmartDSP实时操作系统为参考实时运行。所有以上提到的软件在开发上都能使用ANSI-C语言调用,而且提供完整的开发文档。

简而言之,物理层处理功能包括:调制、信道编码、传输方案、复用、MIMO/分集、信道估测、均衡(3GPP范围之外)。

更多详细资料列举如下:

L1软件包包括

信号处理库:包含LTE L1信号处理管理器和内核库功能。这种信号处理内核是基本的处理单元,而信号处理管理器则是一系列内核的链路集成,包括DL传输信道包、DL物理信道包、UL传输信道包、UL物理信道包。

MATLAB模型包:用于生成测试矢量的已编译的Matlab参考链路。

多核MSC8156上的上行/下行链路功能集成(PDSCH/PUSCH):采用SmartDSP OS实时运行。

在一个典型 LTE 应用中使用 MSC8156

MSC8156 DSP支持广泛的配置组合。需考虑小区规模、上行和下行吞吐量、扇区数量、活跃/已连接用户数量、信号处理算法复杂度(MMSE、SIC等)、天线数量等参数,以决定器件数量和它们的分区。

一个典型的20MHz LTE FDD基站示例将表明一个完整的L1解决方案如何映射到MSC8156上。

典型的基站宏参数考虑如下:一个扇区;小区规模:10km;下行链路 4×4 MIMO;上行链路 2×4 MIMO;4 RX 天线、4 TX 天线;数据速率:下行链路290Mbps,上行链路120Mbps;应用上行链路的MMSE均衡器。

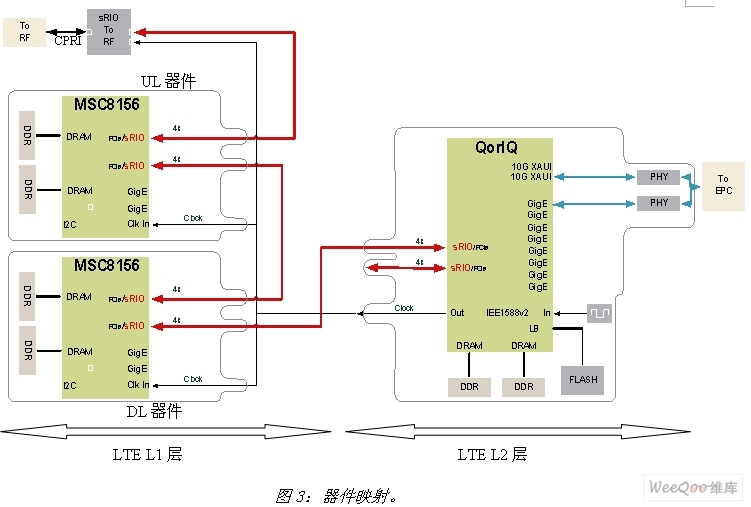

两个MSC8156 DSP实现对LTE物理信道的综合支持。一个器件负责所有上行链路处理,而另外一个被分配负责所有下行链路处理。

下图说明了器件映射的原理。

MSC8156可以通过PCI Express控制器、Gigabit以太网或sRIO连接器连接。sRIO链路以一种串行方式使用,被称为菊花链(daisy chaining)。这省去了对sRIO转换器的需求。

无线频率模块通过CPRI链路连接。一个小型FPGA器件负责从CPRI到sRIO的转换。这是系统中需要的唯一一个FPGA。然后就是链中的上行链路器件,接下来是下行链路器件。此器件被连接到L2器件,在这里被映射到一个QorIQ处理器上。

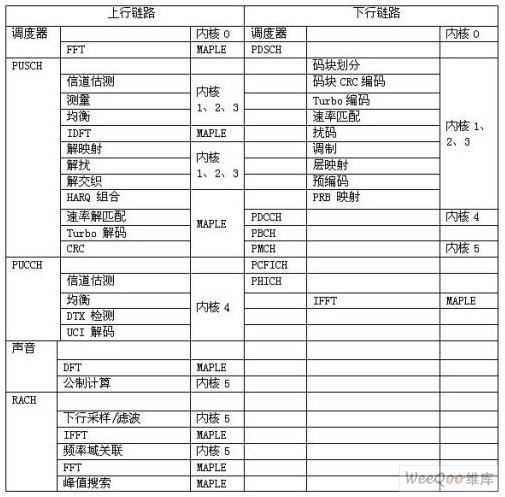

LTE信号处理任务可以在StarCore SC3850内核或MAPLE-B协处理器上执行。一个典型的分区如下所示:

上行链路器件:

3个内核用于共享信道

1个内核用于 随机接入信道(RACH)和声音

1个内核用于控制信道

最后一个内核用作主内核,在其他内核上安排和分配信号处理任务

下行链路器件:

3个内核用于共享信道

1个内核用于控制信道

1个内核用于物理广播信道(PBCH)、物理多播信道(PMCH)、物理控制格式指示信道(PCFICH)和物理HARQ指示符信道(PHICH)

最后一个内核作为任务调度器

下行链路器件的负载通常低于上行链路器件的负载。

下列表格详细列出了内核与MAPLE-B在功能上的分工。

通过这种方法,内核被专门用于预先确定的任务,但是如何分配任务则由调度器负责。为发挥器件能力以便实现1ms的时延要求,该模块具有很高的重要性。

例如,在上行链路器件上,当接收到参考信号的时候,信道估测将首选被分配到内核1、2和3上。然后,当接收到最后的数据符号的时候,可以在三个内核上安排均衡处理。接下来是解映射/解扰以及解交织。通常在空闲时隙安排测量。

上行链路器件利用所有的MAPLE-B处理部件,而下行链路器件仅将其用于最后的快速傅立叶反变换(IFFT)。对于更高的上行链路吞吐量,上行链路器件能够远程利用来自于下行链路器件的Turbo Viterbi处理部件(TVPE)。