1 引言

CCD" title="CCD">CCD (Charge Coupled Devices)电荷藕合器件是20世纪70年代初发展起来的新型半导体 器件。目前CCD作为光电

我们需要对CCD相机所获取的大量高速图像数据进行采集、存储,以便做后续处理和应 用,而进行这一系列信号处理之前,目标信号的获取及所获信号的质量关系到调试整个相机 系统的关键。在调试相机系统时,由于调试的系统总有一些不完善的因素,同时又因为多次 的调试也会增加CCD芯片的风险成本,尤其对于比较昂贵的CCD芯片,调试中如若经常使用将 会带来损坏的风险,因此在调试过程中对CCD芯片输出信号的分析和

2 分析CCD 输出信号的特点

一个 CCD 信号的输出序列由复位脉冲开始,当FET 开关闭合时,图1 中的传感器电容上的电压为初始的参考电压值,这个参考电压值被称为复位馈通电平。经过一定的馈通延迟时 间后,这个电压值降低,成为真正的复位电平。此时,FET 开关打开,则像素电荷被转移到 这个电容上,相应的改变了电容上的电压值。这个电压值就是参考电平、像素电平以及一些 噪声叠加而成的。当CCD 开始工作读取有效信号时,输出信号在每个复位信号的上升沿时复 位,即在输出信号上出现复位干扰脉冲1,然后回到参考电平2,开始读取积分得来的是像元 信号3。实际像素宽度为3 的宽度,1、2、3 的宽度和为一个像素周期,每个像素的信号幅 度为2 和3 的高度差,这些都是CCD 输出信号的重要参数。CCD 输出的信号中包含了较大的 直流分量。直流偏置电压是CCD 正常工作所不可缺少的,其值在几伏到十几伏范围内变化, 并且只消耗几毫安以下的电流,很容易由稳压电源必要时经电阻或电位器分压以及电容滤波 得到。

图1 CCD输出信号

3 硬件结构

整个系统由数字信号发生模块、数模转换模块和输出处理模块3部分构成。选取CPLD以构成 信号发生模块,充分利用它的可编程性,构造出CCD在各种复杂环境下的采集数据,同时生 成与数据信号相匹配的控制信号,控制下级数模转换模块的工作。数模转换模块接收上级发 送过来的数据和控制信号,在控制信号的控制下将数据转换为模拟信号输出。由于该模块的 转换输出为电流,所以还需要增加一个转换模块将电流转换为系统所需要的电压信号,同时为了满足系统对信号精度的要求,还需要增加有源和无源滤波电路模块。系统框图如图2所示,晶振作为CPLD的时钟信号(clk)输入,其它的信号均由其产生。

图2系统原理框图

主要工作分为以下几个方面:

(1)信号发生模块

利用 VHDL 语言设计CCD 输出图像信号和时序控制信号,输出信号有模拟出来的数字图 像信号(10 位并行输出)和时序控制信号,主要包括:相关双采样信号,A/D 采样所需时序 脉冲信号,行、场同步脉冲信号等。

(2)数模转换模块

将模拟的数字信号经由数模

(3)输出处理模块

对由

4 信号发生模块CPLD 的设计

4.1选择符合要求的CPLD

本设计采用LATTICE公司的ispLSI1032e CPLD,该芯片共有84个引脚,可用门数达6000 个,192个逻辑单元,可单独配置为输入、输出及双向工作方式,64个通用I/O口,其传输延 时为7.5ns,最高工作率高达125MHz,可以满足本设计的要求。该系统要求的输出频率为11MHz的相关双采样形式的CCD信号,并且对信号的时序有着严格的要求,选用66MHz的晶振,作为 CPLD的时钟输入。

4.2 程序设计

输出的数字信号要提供给图像传感器的下一级采样系统,符合一定的时序要求,采样所 需时序脉冲信号,输出信号有模拟CCD 输出信号,相关双采样信号,故需要A/D 采行同步脉 冲信号等。信号发生模块CPLD 部分,我们除了需要产生所有的数字信号之外,还需要为下一部分的数模转换模块准备好需要的数据和D/A 时钟时序。

在利用 VHDL 语言在isp 环境下编程、仿真、调试,得到几幅模拟灰度图像和行、场同步信号。输出信号有数字图像信号(10 位并行输出),D/A 的时钟信号(clock1)和写信号 (wrt),相关双采样信号,行、场同步脉冲信号等。输入时钟信号(clk)为66MHz,行同步信号row 用来保证输出像元的同步。

它的输出作为模拟CCD 数据产生和D/A 转换控制模块的时钟输入。模拟CCD 数据产生 模块输出的方波信号ccdout[9..0],经过DAC 变换后,生成CCD 的模拟输出信号。D/A 转 换控制模块生成DAC 的写信号WR 和时钟信号CLK,要求D/A 在数据ccdout[9:0]的一个周 期内采样转换高低电平各一次,需要wrt 和clock1 在ccdout[9..0]的高低电平处分别采样, 为保证clock1 与wrt 信号的相位关系,令wrt 信号在clk 的上升沿变换,clock1 信号在clk 的下降沿变换,这样就产生了我们所需要的数据和控制信号。

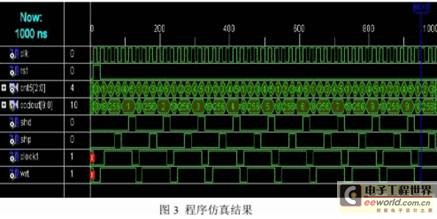

4.3 仿真结果

本设计实现了采用VHDL硬件编程语言和CPLD产生系统的数据源信号,包括模拟CCD输出 的模拟信号产生前的一组数字信号和用于下一级所需要的的控制时序,保证了系统输出信号 的速度和相位关系。如图3的仿真波形所示,ccdout[9..0]为模拟的图像信号,shp、shd为 相关双采样信号,clock1、wrt为下一级数模转换模块D/A的控制信号。参考脉冲shp和视频 脉冲shd在一个像元间隔分别采样一次,最终输出信号为采集到的参考电平与视频电平之间 的差值,采用相关双采样技术可以滤除叠加在输出信号上的复位噪声。