摘 要: 分析了I2C串行总线的数据传输机制,用VHDL设计了串行总线控制电路,其中包括微处理器接口电路和I2C总线接口电路。采用ModelSim Plus 6.0 SE软件进行了前仿真和调试,并在Xilinx ISE 7.1i开发环境下进行了综合、后仿真和CPLD器件下载测试。 结果表明实现了I2C串行总线协议的要求。

关键词: I2C串行总线控制器 接口电路 VHDL CPLD

串行总线和并行总线相比具有结构简单、占用引脚少、成本低的优点。常见的串行总线有USB、IEEE1394、I2C等,其中I2C总线具有使用简单的特点,在单片机、串行E2PROM、LCD等器件中具有广泛的应用。

I2C(Inter IC BUS)是Philips公司开发的用于芯片之间连接的总线。 I2C总线用两根信号线进行数据传输,一根为串行数据线(SDA),另一根为串行时钟线(SCL)。I2C总线允许若干兼容器件(如存储器、A/D转换器、D/A转换器、LCD驱动器等)共享总线。I2C总线理论上可以允许的最大设备数,是以总线上所有器件的总电容(其中包括连线本身的电容和连接端的引出电容)不超过400pF为限,总线上所有器件依靠SDA线发送的地址信号寻址,不需要片选线。任何时刻总线只能由一个主器件控制,各从器件在总线空闲时启动数据传输。I2C总线数据传输的标准模式速率为100kbps,快速模式速率为400kbps,高速模式速率为3.4Mbps。

用VHDL和CPLD设计数字系统具有传统方法无可比拟的优越性,它已经成为大规模集成电路设计最为有效的一种手段。为简单起见,本文采用VHDL设计标准模式的I2C总线控制电路。

1 I2C总线上的数据传输

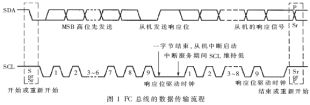

I2C总线包含时钟线SCL和数据线SDA两条连线,SCL由主机产生。I2C总线的数据传输流程如图1所示。其传输过程为:首先主机产生起始位,然后传送第一个字节。8位数据中首先传送的是数据的最高位MSB,最低位LSB为读写指示位,1表示主机读,0表示主机写,高7位地址可使主机寻址128个从器件。

从机收到第一字节数据后发响应位,主机收到响应位后接着发送第二个字节的数据。数据发送完毕后产生结束位,数据传送结束。数据传送时,只有时钟SCL为低电平时SDA才允许切换,SCL为高电平时SDA必须稳定,此时SDA的电平就是总线转送的数值。

在SCL为高电平时,SDA线由高到低切换表示起始位,SDA线由低到高切换表示停止位。起始位和停止位由主机产生,在起始位产生后总线处于忙状态,停止位出现并经过一定时间后总线进入空闲状态。发送器每发送一个字节后,接收器必须产生一个响应位。响应位的驱动时钟由主机产生则接收器将SDA线拉低产生响应位。如果主机是接收器,则接收最后一个字节时,响应位为1,通知从机结束发送,否则响应位为0。当从机不能响应从机地址(例如它正在执行一些实时函数,不能接收或发送)时,或响应了从机地址但在传输一段时间后不能接收更多的数据字节,此时从机可以通过响应位为1通知主机终止当前的传输,于是主机产生一个停止位终止传输,或者产生重复开始位开始新的传输。

SDA线上传送的数据必须为8位,每次传送可以发送的字节数量不受限制。如果从机要完成一些其他功能(例如执行一个内部中断服务程序)才能接收或发送下一个数据字节,则从机可以使SCL维持低电位,迫使主机进入等待状态。从机准备好接收或发送下一个数据字节时,释放SCL,数据传输继续。

SDA和SCL都是双向线路,使用时通过上拉电阻连接到电源。总线空闲时这两条线路都是高电平,连接到总线的器件的输出级必须是漏极开路或集电极开路,这样总线才能执行“线与”的功能。

主机发完第一个字节后,数据传输方向的变化可能存在三种情况。(1)传输方向不变,如主机向从机写;(2)传输方向改变,如主机从从机读数据;(3)传输方向改变多次,如主机对从机进行多次读写。

2 时钟同步与仲裁

I2C总线在任何时刻只能有一个主机,当I2C总线同时有两个或更多的器件想成为主机时,就需要进行仲裁;时钟同步的目的就是为仲裁提供一个确定的时钟。时钟SCL的同步和仲裁通过“线与”来执行,SCL的低电平时间取决于低电平时间最长的主机,高电平时间取决于高电平时间最短的主机。

仲裁过程在数据线SDA线上进行,当SCL为高电平时,如果SDA线上有主机发送低电平,则发送高电平的主机将关闭输出级。因为总线的状态和自身内部不一样,于是发送低电平的主机赢得仲裁。仲裁可以持续多个位,在实际通信过程中,仲裁的第一阶段比较地址位,如果多个主机寻址同一个从机,则继续比较数据位(主机是发送机)或响应位(主机是接收机)。由于I2C总线上的地址和数据由赢得总线的主机决定,因此仲裁过程中不会丢失信息。如果一个主机具有从机功能,则当它失去仲裁时,必须立即切换到从机状态,因为它可能正在被其他主机寻址。

3 I2C总线控制器设计

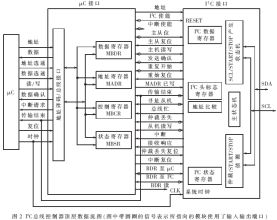

I2C总线控制器的主要作用是提供微控制器(μC)和I2C总线之间的接口,为两者之间的通信提供物理层协议的转换。在串行应用系统中,外围器件(如串行E2PROM、LCD、实时钟等)连接在I2C总线上,再通过I2C总线控制器和μC连起来。其典型的应用,如现在许多彩电的控制系统都基于I2C总线。为了使设计清晰明了,本文将控制器的设计分成两部分。一部分为微控制器(μC)接口,另一部分为I2C接口,如图2所示。

μC接口部分主要包含状态寄存器(MBSR)、控制寄存器(MBCR)、地址寄存器(MADR)、数据寄存器(MBDR)和地址译码/总线接口模块。状态寄存器指示I2C总线控制器的当前状态,如传输是否完成、总线是否忙等信息。控制寄存器是μC控制I2C总线控制器的主要途径,通过置0/1完成I2C总线控制器使能、中断使能、主/从(Master/Slave)模式选择、产生起始位等操作。地址寄存器保存着I2C总线控制器作为从机时的地址。数据寄存器用于保存接收的数据或是待发送的数据。

I2C接口的核心是主状态机,它控制着整个I2C接口的运作。和I2C总线直接相连的模块有起始/停止位产生模块、I2C Header寄存器、I2C数据寄存器和仲裁及起始/停止位检测模块。当控制器是Master时,起始/停止位产生模块用于在I2C总线上产生起始位和停止位;I2C数据寄存器用于保存总线上传送的数据;仲裁及起始/停止位检测模块的作用是执行仲裁,并检测I2C总线上的起始/停止位,以便为主状态机提供输入。其他模块包括:I2C状态寄存器,用于记录I2C总线的状态;地址比较模块,用于比较总线上传送的地址和本机的从机地址是否一致,如果一致,说明其他主机正在寻址本控制器,控制器必须立即切换到从机状态,同时发出响应位。

3.1 μC接口设计

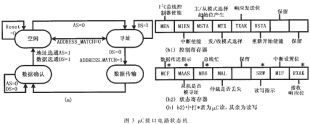

μC接口用于连接I2C接口电路和μC,主要实现两者之间的信号交互握手机制。设计时可以用VHDL提供的状态机来描述信号交互机制中的工作状态切换,如图3(a)所示。

μC接口电路中使用的四组寄存器的地址是24位的,高16位为I2C总线控制器的基址(MBASE),占用μC的地址空间,低8位用于区别不同的寄存器。寄存器本身是8位的,图3(b1)为控制寄存器,图3(b2)为状态寄存器。图中示出了每一位的含义。

3.2 I2C接口设计

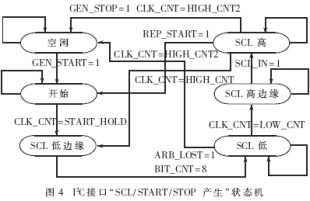

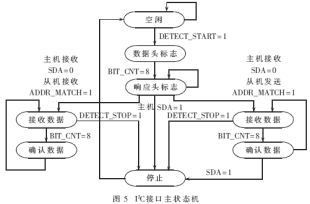

I2C接口用于连接μC接口电路和I2C总线,由两个状态机构成:一个是I2C接口主状态机,用于执行发送和接收操作;另一个为“SCL/SDA/ STOP 产生”状态机,当I2C总线控制器为主机时,这个状态机产生SCL/START/STOP信号。

I2C接口用于I2C总线的驱动和接收,当I2C总线控制器为主机时,I2C接口必须按I2C总线规范驱动总线;当总线控制器为从机时,I2C必须能正确接收满足I2C总线规范的信号。I2C设计规范对总线的时序作了详细的定义,在不同模式下这些参数的具体数值都有明确的规定。“SCL/START/STOP 产生”状态机的状态转换如图4所示, I2C接口主状态机的转移图如图5所示。

4 仿真与硬件实现

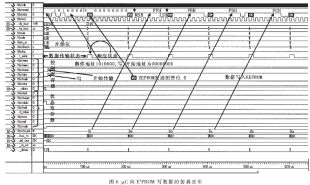

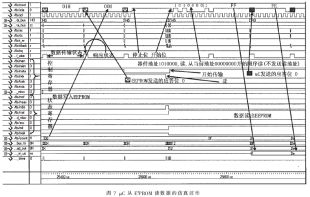

本文中仿真工具采用Mentor公司的ModelSim Plus 6.0 SE,其显著的优越性能是提供了一个混合语言仿真环境,已在产业界广泛应用。为了测试验证系统的功能,本文采用了Atemel公司提供的采用I2C总线协议的AT24C02 E2PROM芯片(256B 8bit)的VerilogHDL仿真模型(AT24C02.v)作为从器件对象,用VerilogHDL语言构建了testbench(测试向量),对所设计I2C总线控制器进行仿真。

图6和图7为μC通过I2C总线控制器对E2PROM进行数据写/读的仿真波形(将数据FFH~0HH写进地址0~255单元,然后将它们再按顺序读的模式读出)。往E2PROM写入时需要给出所写起始单元的地址(图6中为00H); 从E2PROM顺序读时不用给出起始单元地址而从当前地址处开始读(本文中写完256B数据后,地址指针又回到0处)。相关状态及数据已在图中作了标示。由此可见,所设计的总线控制器完全符合标准I2C串行协议的时序要求。

本文设计的系统实现平台采用Xilinx公司的XC95216-10-PQ160 CPLD芯片,总逻辑门个数为4 800。经综合、适配、布局布线后占用器件资源的情况为:宏单元120/216(56%)、寄存器111/216(52%)、功能块331/432(77%)、乘积项分配器544/1080(51%)。可见,系统占用约一半的资源,相当精简。整个系统下载到CPLD后在2MHz时钟频率下运行正常。

参考文献

1 王 诚,薛小刚,钟信朝. FPGA/CPLD设计工具Xilinx ISE使用详解.北京:人民邮电出版社,2005:439~478

2 刘 韬,楼兴华. FPGA数字电子系统设计与开发实例导航.北京:人民邮电出版社,2005:84~126

3 夏宇闻. 复杂数字电路与系统的Verilog HDL设计技术. 北京:北京航空航天大学出版社,1998:110~136