引言

便携式MP3播放器作为一种集音频播放、数据存储为一身的数码产品,其功能结构为电子设计人员所津津乐道。新功能的MP3播放器不断地更新换代。为了满足MP3播放器功能新增的需求,我们设计了一套基于CoolRunner CPLD的软硬件开发系统,制作相应开发板,探索了一种快速实现的方案。

MP3应用开发板的选型和设计

主控模块芯片及其外围器件

XCR3256是Xilinx公司开发的CoolRuner CPLD芯片,可实现6000门的数字逻辑电路,内嵌256个宏单元,支持4个全局时钟,具有低功耗、可快速ISP、延时可预测等特点,可满足MP3功能和数码产品方面的一些特殊要求,我们选用XCR3256芯片实现M P3主控模块。该主控模块用于对各外围器件的控制,协调各外围器件的工作。外围器件主要有解码芯片组(MAS3507D和DAC3550A)、Flash存储器、LCD、USB接口、并口等。主控模块与各外围器件的框图如图1所示。

图1 MP3应用开发板结构框图

主控逻辑单元是整个主控模块的核心部分,决定着MP3播放器各功能,如播放、快进、下载之间的优先度和顺序,为其他逻辑单元提供实现更加复杂操作的控制信号。主控逻辑单元通过状态机对其他模块进行控制,其状态机如图2所示,该图详细地描述了MP3播放器不同工作阶段的操作条件和各阶段之间的切换情况。

特别需要说明的是:①LOW_PWR使DAC3550A工作在低功率模式下;②IDLE是播放与下载、快进、后退等操作之间的转换状态;③UPDATE_TRACK将歌曲曲目更新,并传递给LCD显示。

图2 主控逻辑单元状态机

DAC3550A是一款专为音频应用而设计的高精度数模转换芯片,具有低功耗操作模式,连续采样频率从8KHz到50KHz均可自主选择,这就给设计带来了极大的灵活性;还提供了简洁的I2S总线接口和I2C总线接口,主控模块正是通过I2C总线对DAC3550A三个寄存器AVOL(16bits)、GCFG(8bits)、SR_REG(8bits)写入相应命令而实现控制的。DAC3550A接口电路图设计如图3所示。

图3 DAC3550A接口电路图

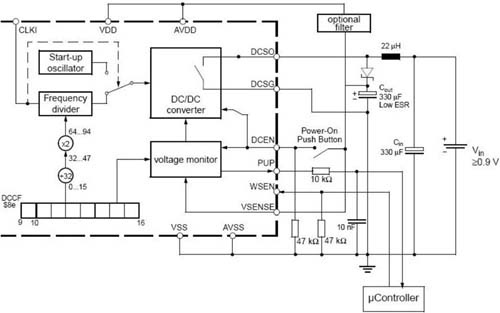

MAS3507D可实现2阶或3阶的MPEG音频解码功能,内嵌的功率管理器可降低低采样频率时的功率,并可以在芯片闲置时将其暂时断电(power off)。该芯片还可以对音效进行调整,以满足用户不同需求;为输出音频数据而提供的I2S总线端口使MAS3507D和DAC3550A的连线更加简洁方便。MAS3507D是通过给主控模块的反馈实现对DAC3550A输入控制的,MAS3507D DC/DC转换接口电路如图4所示。

图4 MAS3507D DC/DC转换接口电路

开发板工作流程

MP3应用开发板的工作流程为:

上电→提取用户命令→读存储器→将MP3音频文件送至MAS3507D进行解码→解码后的数字信号经DAC3550A数模转换→模拟信号输入耳机。

性能设计

设计过程中,为满足今后功能扩展及增强开发平台系列化的需要,我们对开发板的功能布局做了很多调整。

我们将CoolRunner芯片与解码芯片组连接的引脚设计成插针形式,可及时更新和选用新的解码芯片组,而解码芯片组决定着MP3播放器所能播放音频文件的格式及音质。低功耗是MP3播放器追求的一项重要指标,开发板中选用的XRC256XL芯片及解码芯片组(MAS3507D和DAC3550A)均满足了低功耗的要求。

布线要点

MP3应用开发板的设计软件我们选用ProtelDXP。在布线时,我们注意到一些问题,如I2C总线在高电平时对串扰和干扰的高度敏感性要求在总线或带状传输线超过10cm并且包含VDD和VSS时,布线必须按SDA、VDD、VSS和SCL从上到下的顺序进行;对MAS3507D和DAC3550A之间负责数据传输的I2S总线应尽量减少布线长度,并且避免周围信号线的干扰。

MP3应用开发板的调试

我们设计了一个描述MP3主控模块的IP Core,特别注意到了USB端口的下载功能及歌词与音频的同步显示功能。

调

试环境

仿真和综合过程中,我们使用的EDA工具有:Xilinx公司开发的ISE 6.2,Synplicity公司的Synplify Pro7.3以及Mentor Graphics公司的Modelsim SE5.7e。

调试流程

关键的测试流程如下:

(1)在ISE6.2下将修改后的IP Core编译通过,编写测试文件。用Modelsim SE5.7e进行功能仿真。该测试文件比较全面地考虑了实际情况,例如对I2C总线的数据线SDA和时钟线SCL增加了上拉模块PULLUP,以模拟实际中上拉电阻对I2C总线的上拉作用。该测试文件很好地模拟了主控模块对各外围器件的控制,全面反映了开发板的工作情况,并且是在硬件制作完成之前就对主控模块进行功能和时序上的仿真验证,除了证明了源代码功能上的正确性和时序上的精确性,同时还大大缩短了设计周期。

(2)调用Synplify Pro7.3对MP3主控模块的源代码进行综合,生成网表文件及布局布线约束文件等。

(3)利用ISE 6.2将网表中的逻辑符号门组装到物理元件(CLB和IOB)中,并将元件放置到器件中进行连接,同时提取出时序数据并生成各种报告。

(4)利用在布局布线中获得的精确参数再次验证电路的时序,调用Modelsim SE5.7e进行后仿真。

(5)烧写验证。编写UCF(User Constraints File)文件mp3.ucf,设置好全局约束、端口约束等,然后使用ISE集成的配置工具iMPACT,生成PROM格式的配置文件,再将其通过JTAG端口下载至自行设计成功的MP3应用开发板。在MP3音频文件被下载至FLASH存储器后,就可以对该IP Core进行调试。经调试,我们所预期的功能如播放、快进、后退、静音等,均得到的实现,表明调试成功。

结语

本文介绍了基于CoolRunner CPLD的MP3应用开发板的设计流程,验证了利用现有IP Core设计的可行性和高效性。在设计过程中,硬件(实验评估板)的设计和基于IP Core的算法设计可同步进行,避免了两者因异步带来的设计周期的延长。实践证明本文的设计思路和实现方法是一种灵活、快速、可靠地开发数字系统平台的设计方案。

参考文献:

1. 王诚,薛小刚,钟信潮 FPGA/CPLD设计工具─Xilinx ISE5.x使用详解,人民邮电出版社,2003.

2. 金西 VHDL与复杂数字系统设计,西安电子科技大学出版社, 2003.