摘 要: 提供了基于CPLD" title="FPGA/CPLD">FPGA/CPLD的数字化音频处理系统的典型解决方案。该方案由语音芯片(TLV320AIC23)和处理器(FPGA/CPLD)两部分组成。语音芯片完成模拟语音信号与数字信号之间的相互转换,包括ADC和DAC;处理器则完成对经模数转换后的语音信号在数字域处理的过程。该方案可以充分发挥FPGA/CPLD所具有的灵活性好、实时性能高及并行处理能力强的特点。

关键词: 语音处理 音频编解码器 FPGA SPI DSP-Mode

随着人们消费水平的提高和全社会信息化、数字化程度的加快,数字化音频处理被广泛应用于各个领域。需要语音系统完成的功能越来越复杂,如语音加解密、语音识别、语音录放、数字音效处理等;同时,对语音质量的要求也越来越高,因此对语音芯片和处理器提出了更高的性能要求。

TLV320AIC23是TI生产的集成模拟功能的高性能立体声音频编解码器[2],而FPGA/CPLD有着强大的数字逻辑处理功能,并凭借其灵活性好、实时性高等特点在业界的应用越来越广。本文设计并实现了基于TLV320AIC23与FPGA/CPLD的数字化语音处理系统。

1 系统方案介绍

图1所示数字化语音处理系统中,主要包括模拟语音信号采集、模数转换器(ADC)、接收模块(RX)、数字语音信号处理、发送模块" title="发送模块">发送模块(TX)、数模转换器(DAC)以及模拟语音信号输出。其中模拟语音信号采集、模数转换器(ADC)、数模转换器(DAC)和模拟语音信号放大部分的功能可以由语音专用芯片完成;接收模块(RX)、数字语音信号处理和发送模块(TX)部分的功能则由处理器完成。

1.1 语音芯片的选择

目前市场上的语音芯片种类繁多,各有特色。本系统从便携性、移动性、高性能和低功耗等方面综合考虑选用了TLV320AIC23[2]。此款芯片采用低功耗设计,各个功能模块均有断开功能,录放模式下功率消耗小于23mW,并且具有TI特有的MicroStar JuniorTM封装方式,占用的PCB面积仅为25mm2。另外这款芯片的ADC与DAC采用多位的∑-△技术,并且内部集成高采样率的数字内插滤波器,传输字长可以是16、20、24、32位,支持8kHz-96kHz的采样率[2]。ADC的信噪比可达90dB,DAC的信噪比可达100dB,从而可在小型低功耗设计中实现高保真录放音[2]。

1.2 处理器的可选方案

MCU:通常的MCU数据处理能力较低,接口资源有限。

DSP:DSP的数据处理能力强,工作频率高;与TLV320AIC23的控制和数据传输接口可以直接匹配,但需要占用DSP有限的接口资源,且芯片成本相对较高。

FPGA/CPLD:接口设计灵活,具备用户自定义端口功能,并行处理能力强[1]。

本文要实现数字语音处理系统的通用平台,从可扩展性、设计灵活性和成本等方面综合考虑,FPGA/CPLD是比较理想的选择。但是在基于FPGA/CPLD与TLV320AIC23的数字语音处理系统中,由于TLV320AIC23和FPGA/CPLD之间没有现成可用的固定接口,因而接口部分是系统设计和实现过程中的重点和难点。

2 数字化语音处理系统中硬件电路设计

2.1 语音芯片电路

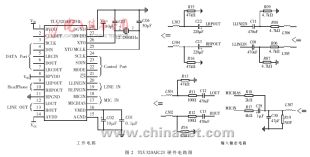

TLV320AIC23内置耳机输出放大器,支持MIC和LINEIN两种输入方式(二选一),且通过对相应寄存器设置可调节输入和输出的增益。TLV320AIC23具有11个可编程控制寄存器,通过不同的设置,可以改变芯片的工作状态。控制接口具有SPI(三线)和I2C(两线)两种工作方式,由MODE引脚选择:MODE=0为I2C模式,MODE=1为SPI模式。TLV320AIC23与数字系统的数据传输接口支持4种数据格式:左对齐模式、右对齐模式,I2S模式和DSP模式[2]。

TLV320AIC23的硬件电路如图2所示。外围模拟电路包含了MIC、LINEIN的输入电路和LINEOUT、HEADPHONE的输出电路,实现过程中两路输入是二选一的,两路输出并行。

2.2 FPGA/CPLD与TLV320AIC23连接电路

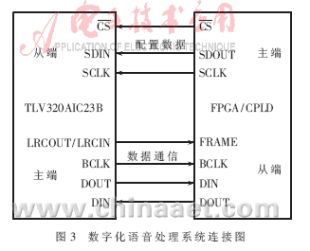

根据TLV320AIC23使用规则,需要提供控制接口和数据通信接口[2]。控制接口选择SPI方式,即TLV320A-IC23需要通过CS、SDIN、SCLK三线与FPGA/CPLD连接[2]。由FPGA/CPLD发送控制字" title="控制字">控制字到TLV320AIC23控制寄存器,使其按照寄存器设置进行工作。数据通信接口选择DSP模式传输数据,设置TLV320AIC23为主(Master)模式,FPGA/CPLD为从(Slave)模式。由文献[3]可知,工作在Master模式下的TLV320AIC23将时钟信号BCLK和帧同步" title="帧同步">帧同步信号LRCOUT、LRCIN提供给工作在Slave模式下的FPGA/CPLD。

工作电路中,TLV320AIC23外接12.288MHz晶振,内部ADC和DAC的采样率设置为32kHz,数据字长为16位[2]。FPGA/CPLD以Altera公司器件EP1C3T144C8为例。系统连接结构如图3所示。

3 用VHDL实现FPGA/CPLD和TLV320AIC23的接口设计

3.1 控制接口

(1)时序分析

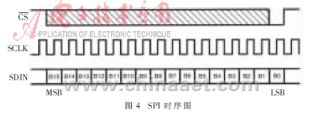

SPI是一种同步串行接口,能实现全双工通信,一般需要四线支持,即片选信号 、时钟信号SDCLK、主入从出信号MISO和主出从入信号MOSI。配置TLV320A-IC23的控制时序工作在单向SPI方式下,只需三线;工作在Master模式下的FPGA输出:片选信号

、时钟信号SDCLK、主入从出信号MISO和主出从入信号MOSI。配置TLV320A-IC23的控制时序工作在单向SPI方式下,只需三线;工作在Master模式下的FPGA输出:片选信号 、时钟信号SCLK和数据输出信号SDOUT;工作在Slave模式下的TLV320AIC23三线均为输入。SPI的时序如图4所示[2]。

、时钟信号SCLK和数据输出信号SDOUT;工作在Slave模式下的TLV320AIC23三线均为输入。SPI的时序如图4所示[2]。

每一个控制字由16位数据构成:7位地址[15..9]和9位数据[8..0],按照高位(MSB)在前的顺序传输[2]。每一位数据在SCLK的上升沿" title="上升沿">上升沿锁存进TLV320AIC23接收移位寄存器,每一个控制字发送结束时, 要产生一个上升沿。

要产生一个上升沿。

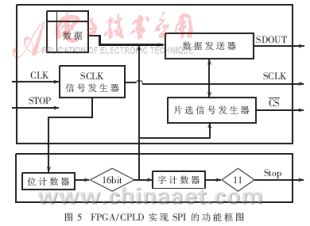

(2)实现方案

FPGA/CPLD实现SPI的功能框图如图5所示。SPI实现模块包括两个部分,即信号生成模块和计数控制模块。信号生成模块输出SCLK、 和DATA信号,其中SCLK是通过对CLK时钟分频生成的恒定时钟信号,它为片选信号发生器(

和DATA信号,其中SCLK是通过对CLK时钟分频生成的恒定时钟信号,它为片选信号发生器( _Generate)和数据发送器(DATA_Sending)部分提供工作时钟。计数控制模块包括位(Bit)计数器和字(Word)计数器。位计数器用于记录串行发送数据个数,字计数器用于记录已发送控制字的个数。当FPGA/CPLD对TLV320AIC23的所有11个寄存器配置完成后,输出停止整个控制字传输模块工作的标志信号Stop。

_Generate)和数据发送器(DATA_Sending)部分提供工作时钟。计数控制模块包括位(Bit)计数器和字(Word)计数器。位计数器用于记录串行发送数据个数,字计数器用于记录已发送控制字的个数。当FPGA/CPLD对TLV320AIC23的所有11个寄存器配置完成后,输出停止整个控制字传输模块工作的标志信号Stop。

为保证TLV320AIC23的SPI正常工作时序,FPGA/CPLD在SCLK的下降沿处通过SDOUT输出数据位。在控制字最后1位数据输出完成后的SCLK下降沿处, 产生一个上升沿,结束一个控制字的传输并将下一个待发送的控制字锁存到FPGA的发送移位寄存器中。当对TLV320AIC23的所有寄存器配置结束时,STOP信号产生一个上升沿,停止整个控制字传输模块的工作,同时打开数据传输模块,开始FPGA与TLV320AIC23的数据传输和音频信号的数字处理过程。仿真时序如图6所示。须注意的是计数器的递增操作和对计数器值的判断要分别在SCLK下降沿和上升沿进行,避免产生竞争。

产生一个上升沿,结束一个控制字的传输并将下一个待发送的控制字锁存到FPGA的发送移位寄存器中。当对TLV320AIC23的所有寄存器配置结束时,STOP信号产生一个上升沿,停止整个控制字传输模块的工作,同时打开数据传输模块,开始FPGA与TLV320AIC23的数据传输和音频信号的数字处理过程。仿真时序如图6所示。须注意的是计数器的递增操作和对计数器值的判断要分别在SCLK下降沿和上升沿进行,避免产生竞争。

3.2 数据通信接口

(1)时序分析

通过配置TLV320AIC23,使其数据接口工作在DSP模式。在DSP模式下工作的TLV320AIC23参与数据通信的信号有:两个帧同步信号输出LRCIN和LRCOUT、时钟信号输出BLCK以及数据输入和输出信号DIN、DOUT[2]。由于工作在主模式下的TLV320AIC23的两个帧同步信号完全一致,因而工作在Slave模式下的FPGA只需一个帧同步信号输入。

DSP模式时序图如图7所示[2]。由此分析得出,TLV320AIC23在帧同步信号下降沿到来时开始传输数据,在时钟信号BCLK下降沿时,DIN和DOUT同时变化,双向传输数据,以先传输左声道语音数据后传输右声道语音数据(由控制字选择)的顺序与FPGA进行通信。

为保证数据传输的正确性,在BCLK的上升沿,FPGA/CPLD读取TLV320AIC23的输出数据(DOUT);在BCLK的下降沿,FPGA/CPLD写数据到TLV320AIC的数据输入端(DIN)。

(2)实现方案

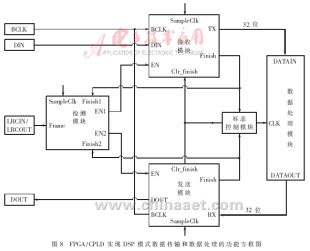

由FPGA/CPLD实现DSP模式数据传输和数据处理的功能框图如图8所示,它由五部分组成:检测模块、数据接收模块、数据发送模块、标志控制模块和数据处理模块。其中检测模块用于检测帧同步信号,并使能数据接收模块和数据发送模块;数据接收模块和数据发送模块在使能信号有效的情况下分别启动数据接收和发送操作,传输时钟都是BCLK;标志控制模块用于在一帧数据发送和接收完成后,复位接收模块和发送模块,使其等待下一个帧同步信号的到来;数据处理模块将接收到的并行数据经过数字域处理后转发给发送模块。

在功能框图中接收模块(RX-Module)和发送模块(TX-Module)的使能信号不同:对于接收模块,使能信号在帧同步信号(LRCIN/LRCOUT)的下降沿产生,在此后的BCLK上升沿处读取数据,存放到接收寄存器中,如果一帧数据已经接收完毕,则下一个BCLK的下降沿输出完成信号(finish)。在BCLK的下降沿计数器计数,记录在前一个BCLK上升沿读取的数据的个数。这种处理方式避免了竞争,保证在判断时计数器值处于稳态,数据最后一位输出稳定后关闭传输模块。而对于发送模块,被发送的数据在BCLK的下降沿输出,所以使能信号在帧同步信号(LRCIN/LRCOUT)的上升沿产生。SampleClk是一个高频扫描信号,用于检测帧同步信号,采用高频信号检测低频信号可以减少毛刺的引入。

基于本文所述的方案成功实现了Altera EP1C3T144C8对TLV320AIC23的配置、两者间的数据通信以及对语音数据的处理,从而建立了由语音AD采集、传输、处理和DA语音输出四个部分组成的结构化数字语音处理系统开发平台。本文通过对设计方案的分析与实现得出:在FPGA/CPLD中设计数据接口非常灵活,可按功能划分模块,由标志信号控制模块启闭,方便设计和调试。本文为基于FPGA/CPLD和TLV320AIC23的数字化语音处理提供了完善的、高扩展性的解决方案,通过改变数字处理模块的功能即可实现各种数字语音系统,如语音加密/解密、语音数据存储、语音压缩、数字音效处理等。

参考文献

[1] WOLF W.FPGA-BASED System Design.Prentice Hall,2004.

[2] Texas Instrument Inc.TLV320AIC23B Stereo Audio CODEC 8- to 96-kHz,With Integrated Headphone Amplifier.

2004,2.