TPC码译码器硬件仿真的优化设计

2008-07-21

作者:郭 丽,蒋卓勤

摘 要: 介绍一种TPC码迭代译码器" title="译码器">译码器的硬件设计方案,基于软判决译码规则,采用完全并行规整的译码结构,使用VHDL硬件描述语言,实现了码率为1/2的(8,4)二维乘积码迭代译码器,并特别通过硬件测试激励来实时测量所设计迭代译码器的误码率情况,提出了优化设计方案,和传统的硬件仿真" title="硬件仿真">硬件仿真方法相比大大提高了仿真效率。仿真结果证明该译码器有很大的实用性和灵活性。

关键词: TPC码 软判决译码 外信息 迭代译码 VHDL FPGA

1993年伴随着著名的Turbo码的提出,法国的RM.Pyndiah于1994年将Turbo软迭代译码的思想应用于早期的乘积码[1]之中,提出了分组Turbo码(BTC)[2],即Turbo乘积码(TPC码),正是从这个时期开始乘积码独特的优点再次得到了编码界的关注。相对于Turbo码而言,Turbo乘积码很好地实现了译码性能与硬件实现的复杂度的折衷,很容易由硬件实现。近年来一些著名的硬件和芯片制造商相继开发出一些针对无线通信应用的乘积码的编译码芯片和相应的IP核,可以说如何有效地设计一个TPC码的迭代译码器已经成为目前国内外围绕Turbo码在无线通信领域中应用的一个重要问题。

本文提出了二维TPC码的迭代译码器的FPGA设计方案,特别建立了FPGA硬件仿真模型" title="仿真模型">仿真模型,大大提高了信道编码硬件仿真效率,为了评估TPC译码器的译码性能好坏,通过改变不同信噪比下的输入激励,可以分析所设计译码器的误码率情况。经过功能验证" title="功能验证">功能验证,译码功能与C程序仿真的功能非常吻合,从而证明了整个设计的合理性,为今后实现更实用、更长码长和更高码率的TPC码译码器做了有益的尝试。

1 编译码原理

构造TPC码的线性分组码很多,如汉明码、单校验码(SPC)、RS码和BCH码等等,目前国际上多采用SPC码和扩展汉明码构造。

为了使设计验证过程不至于繁琐,方便更加清楚地说明问题,这里假定以简单的(3,2,2)单校验码为成员码。对于码长较短、码块小的简单码型可以回避开RM.Pyndiah提出的复杂的修正Chase译码算法[3],而采用Turbo软迭代译码原理,这样可以降低译码复杂度,但译码效果肯定会有所下降。为此做了一些有益的设计尝试。

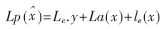

具体算法采用逐位MAP译码规则,最终目的是要得到信息x的最大似然后验信息。最终的译码结果包含三部分独立的似然概率估计值。即:信道软输出、先验概率和外信息[4][5],即:

图1给出了一个简单两维(8,4)TPC码迭代译码的过程。

2 电路设计

2.1 迭代译码核心

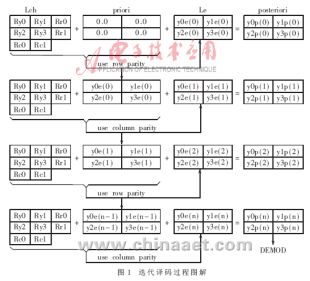

当用FPGA器件实现TPC码的整体译码功能时,迭代译码过程的具体实现主要是行和列外信息计算模块。如图2所示,附加了若干D触发器作为总体控制时序控制模块,进行数据缓冲,保证和协调各个译码模块的连续进行和同步工作。

2.2 功能验证电路

为进一步验证此二维TPC码译码器的纠错性能的好坏,把译码器的输出结果和理论输入进行比较来分析译码器的译码功能是否完善,特别设计了功能验证模块,并编写了测试激励。

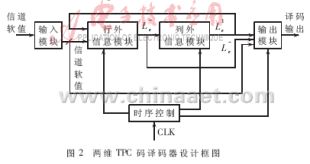

图3为该译码器的功能验证方块图,分为译码控制与输入模块(input)、原始输入参考模块(senddata)、TPC码迭代译码模块(TPC decoder)及误码率计算分析模块(Error Counter)。

3 仿真波形" title="仿真波形">仿真波形

整个TPC码译码器由上述方案中的几个下层文件组成了顶层文件。整个设计采用VHDL语言编写了各个模块的程序代码,各个模块源程序成功通过编译。程序在Xilinx公司的开发工具ISE8.1和与Xilinx公司配套的ModelsimXE 6.0a集成仿真工具的环境下仿真调试通过。图4为该(8,4)二维乘积码的译码性能功能仿真波形,其中时钟信号CLK周期为10MHz,上升沿有效,启动信号START下降沿有效,为8个时钟周期。译码后4bit信息为:y0d、y1d、y2d、y3d。从图4中可见数据的译码输出仿真测试结果波形。

基于硬件仿真模块,在不同的输入测试激励文件的控制下,对应不同的信噪比环境,分别输入各种不同的激励,可以从低噪声一直到非常大的噪声。图4为输入激励为信噪比9dB时输出的波形图,误码率计算分析模块在启动信号start的上升沿采样数据,下降沿则输出误码率统计结果。如图5所示,在输入激励为SNR=9dB时,误码率为7/10000。

可以看出所设计的TPC码迭代译码器具有较好的译码效果,通过改变输入激励部分参数,可以设计出更多码型的TPC码译码器,具有较高的实用价值。

4 几点思考

(1)方案中所建立的功能验证系统是任何信道编码译码器验证测时通用的。该方案完全改变了传统方式,非常值得推广使用。从以往的信道编译码的工程实践看,对于功能仿真测试部分实现方式虽然很多,但是效率低,不直观。通常采用从最后MODELSIM仿真波形文件中提取具体仿真数据,然后对所有数据进行分析归纳统计,最后得出整个误码率情况。这种方法速度慢、精度低。文中所提出的二维乘积码采用的硬件验证系统的建立为译码器的硬件仿真开拓了一个新的高效率思路,不仅仿真速度快,而且通用性强,可以应用到任何信道纠错译码模块的硬件仿真测试系统中去,而且不需要人为分析数据结果,全部过程从Modelsim仿真波形自动读出,精确度非常高。采用硬件FPGA仿真误码率,不仅比软件仿真速度快,而且灵活方便,非常值得推广。

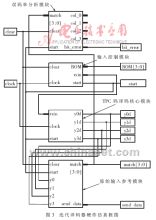

(2)该方案可以做更优化设计,如图6所示。进一步延伸这个考虑,如果补充上TPC编码模块和信道模块(AWGN 和Fading)以及软判决映射器,整个验证系统将更为通用。

其中信息源模块由线性反馈移位寄存器LFSR(Linear Feedback Shift Registers)构成,产生(0,1)序列送入TPC码编码器产生二维码块,随后来自码块的比特数据叠加上来自AWGN或是衰落信道模块产生的噪声后被软判决映射器从(0,1)映射为(-1,+1)比特流,经过串入并出转换后并行输出给TPC码译码器,经译码器译出的信息比特将会和原始输入信息进行异或比较,最后由误码率计算模块输出误码率。

这样一个TPC码验证测试激励系统提供了快速的硬件仿真模型,非常值得推广,相比较利用C程序软件仿真,仿真时间大致为10:1,大大提高了TPC码性能仿真效率。

如何有效地设计一个TPC码的译码器成为目前围绕TPC码的无线通信应用领域的一个重要问题。本文针对短码、小码块的TPC码迭代译码器的FPGA设计,特别建立了TPC 码迭代译码器的硬件仿真模型,大大提高了性能仿真效率,提出了信道编码译码器硬件设计的优化设计方案,作为一种有益的探索和尝试,为下一步实现各种信道编码译码器积累了宝贵经验。该硬件仿真模型的灵活性非常强,通过改变设计中的一些输入和控制参数,可以设计更多IEEE802.16标准推荐的更实用码型和迭代次数的TPC码。

参考文献

[1] ELIAS P.Error-free coding,IRE Trans.on Inf.Theory,vol.IT-4,1954.(9):29-37.

[2] PYNDIAH R,GLAVIEUX A,PICART A,et al.Near optimum decoding of product codes,in proc.of IEEE GLOBECOM′94 Conference,vol.1/3,1994,11~12。

[3] PYNDIAH R.Near optimum decoding of product codes:Block Turbo Codes,IEEE Trans.on Comm.,vol 46,1998(8).

[4] BERROU C,GLAVIEUX A,THITIMAJSHIMA P.Near Shannon limit error-correcting coding and decoding:Turbocodes(1),IEEE Int.Conf.on Comm.ICC′93,vol 2/3,1993(5).

[5] 王新梅,肖国镇.纠错码-原理与方法(修订版).西安:西安电子科技大学出版社,2002.