一种新型H.264 CABAC编码器硬件结构设计

2008-07-21

作者:何 俊,王阳明

摘 要:提出一种基于H.264的上下文自适应二进制算术编码器硬件设计方法。本设计中包含一个由二进制化" title="二进制化">二进制化以及上下文模型组成的14组并行上下文对产生器,一个抓取邻近区块数据的三级流水线结构以及一个内含前馈处理且融合三种模式的四级流水线结构的算术编码器。该算术编码器可以一个时钟处理一个位元" title="位元">位元;整个设计平均每个时钟处理0.77个位元。

关键词:上下文自适应 CABAC H.264/AVC 语法元素

视频编码的最后一步是熵编码" title="熵编码">熵编码,主要应用在对量化变换系数、自适应块变换、运动向量和其他编码信息的压缩技术中。H.264/AVC[1]采用两种类型的熵编码,基于上下文自适应的二进制算术编码(CABAC)和基于上下文自适应的可变长编码(CAVLC)。而CABAC[2]是一种比任何传统熵编码效率都要高的编码法,与CAVLC相比,CABAC能节省6%~15%的位速率。在对CABAC算法分析的基础上,笔者提出一种三级流水线结构实现方法,该方法充分利用高效的并行结构优化CABAC编码器结构。

1 CABAC编码器结构

如图1所示,结构由三大模块构成:二进制化与上下文模型(CM)模块,算数编码(AE)模块,并进串出(PISO)模块。二进制化与上下文模型模块负责产生二进制串及上下文建模[3],其输出为并行的14组上下文对。CM模块中的取邻模块通过取邻地址产生器(AG)生成的地址,从取邻存储器中读取出相邻左宏块" title="宏块">宏块和上宏块中的语法元素(SE)。PISO模块负责收集有效的上下文对,在一个时钟周期" title="时钟周期">时钟周期中将其输出到AE中。PISO模块输入为14组并行上下文对,输出为一组上下文对。AE模块[4]由融合三种模式的四级流水线构成,模块中的表存储器存储初始语法表,片段初始化上下文表子模块负责上下文表的建立。transIdxLPS表和rangeTabLPS表由组合逻辑电路实现,其中上下文表存储器为双端口存储器。本编码器编码开始一段新片段编码时,主控制器首先声明start_slice_cabac寄存器,编码器开始建造上下文表,当其完成后编码器向主控制器发送声明信号end_cabac_build_table,并且等待下一命令。这时编码器开始新宏块编码,并分别从取邻存储器读取相邻区块数据和从mb_info存储中读取宏块SE数据。所有宏块SE数据编码完成后,CABAC编码器开始从coeff_mem存储器中读取残余SE。每完成一个宏块,编码器声明一个end_mb寄存器,当前片段的最后一宏块处理后,编码器则声明一个end_slice_cabac寄存器。

下面分别叙述编码器的CM模块和AE模块。

1.1 二进制化与上下文模型模块(CM)

当前的语法元素通过该模块二进制化,并为每一个二进制串(bin)计算相应的上下文,得到最小的冗余码,如图2所示。首先在一个时钟内完成SE的二进制转换,产生1~14的二进制串,为提高速度使用不查表法;然后根据先前的上区块和左区块编码数据为bin,计算相应的上下文值;最后产生1~14组上下文对。每一组上下文对包括1bit编码位,9bit上下文存储地址位及2bit编码模式位。

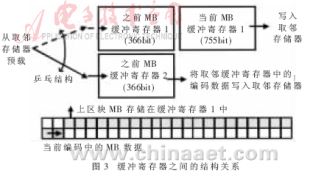

CABAC编码器需要从相邻的左区块、上区块及当前宏区块中提取数据计算上下文值。图3中取邻模块由3个缓冲寄存器构成,编码时编码器将当前被编码的SE写入当前宏区块(MB)缓冲寄存器中,同时将左/上区块数据从取邻存储器中取出,预载入之前MB缓冲寄存器1和2中。

当编码MB是奇数地址时,编码器从取邻存储器中取出左/上区块SE,预载入之前MB缓冲寄存器1中,同时将当前宏区块MB缓冲寄存器中被编码的SE 写入取邻存储器中。该模块可以将之前MB缓冲寄存器2中的相邻上区块数据和当前宏区块MB缓冲寄存器中的相邻左区块数据输出到二进制化与上下文模型模块中计算上下文对的值。

相反,当编码MB是偶数地址时,编码器从取邻存储器中取出左/上区块SE预载入之前MB缓冲寄存器2中,同时将当前宏区块MB缓冲寄存器中被编码的SE 写入取邻存储器中。二进制化与上下文模型模块可以从之前MB缓冲寄存器1和当前宏区块MB缓冲寄存器中获得相邻块数据。

1.2 算术编码器模块(AE)

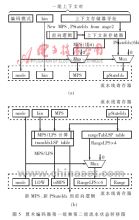

这里提出一种融合3种模式(EncodeRegular,EncodeBypass和EncodeTerminal)的四级流水线结构的算术编码器,如图4。在第一级流水线中,编码器从上下文表存储器中读出MPS和pStateIdx;在第二级中,编码器判定bin是否是MPS并且读取两组合电路表(rangeTabLPS表和transIdxLPS表),得到新的MPS和pStateIdx;在第三级,编码器计算出新的Range和Low;最后在第四级输出编码。同时其内馈前向逻辑更新上下文存储器。

(1)对于整数算数编码,每编码一次后对Range和Low的值都需要再归一化。 经分析,EncodeRegular中储存器访问较耗时,决定由单独一级流水从上下文表储存器中读取数据,并令再归一化前没完成的功能函数都集中到第二级流水阶段完成。图5(a)描述第一级流水线利用上下文存储器地址读取上下文存储器。EncodeRegular时MPS和pStateIdx分别被存储在流水线两个寄存器中。而EncodeBypass和EncodeTerminal时,这两个寄存器被置零,并且在第二级流水中暂不使用,二进制串和编码模式位不做任何修改直接送入下级流水。图5(b)为第二级流水结构。这里使用bin、MPS和pStateIdx来决定二进制串是否是MPS,并把得到的MPS传送到寄存器“isMPS”中,为第三级流水做准备。此级也使用pStageIdx作为索引在rangeTabLPS表中搜索得到4个RangeLPS,并将结果储存到流水线寄存器中。因为EncodeBypass和EncodeTerminal比较简单,把它们主要集中到第一级和第二级中处理。另外,第二级中计算得到的新MPS和新pStatIdx将输入到前向逻辑中,作为后续上下文起始判断条件。

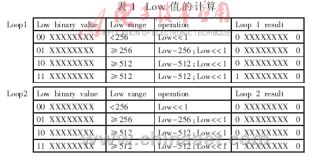

(2)为了得到期望的精确输出,每编码一次后对Range和Low的值都需要再归一化。在H.264的CABAC中需要9bit和10bit分别表示Range和Low。Range值将逐渐变小,因此Range值限定在256~511之间。如果Range值小于256(0x100),Range将再归一化,并紧接再归一化Low。设计PutBit和bitsOutstanding位在第四级进行更新完成重整和输出工作。根据对Range的判断可以得到循环(loop)次数。最大的loop次数是8次。这里对Range和Low的更新要求在一个时钟周期完成,因此设计每循环一次,Range/Low移位一次。

表1描述经过loop1和loop2后的新Low值。根据第一次循环的结果,可以算出:仅仅当源流串的头两位都为1时,loop1结果的第一位才为1。loop2使用loop1的结果。这就意味:如果loop1结果的头两位都为1,loop2结果的第一位也为1。因此根据循环次数就可以判定Low的第一位比特和其余位。如果源流串的前(loop count+1)位都为1,新Low的第一位也将是1;否则,第一位将是0。通过使用这种方法,新Low可以在一个时钟周期计算出来。

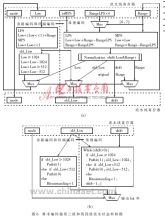

在第三级流水结构中,主要完成Range和Low的更新和逻辑反馈。源流串中的old_Low值及与循环次数有关的shift值都被写入第四级流水线寄存器中,实现PutBit过程。图6(a)为第三级流水,其左框架结构中为EncodeBypass和EncodeTerminal模式的简单运算得到新Low。右框架结构为EncodeRegular有关MPS和LPS的一些简单运算,然后通过normalization shift更新Range和Low值。

第四级流水结构主要实现bit流的输出过程。图6(b)为第四级流水,其左框架结构中为EncodeBypass和EncodeTerminal bit流输出,再归一化后根据old_Low决定下一个输出bit为0或1。右框架结构为EncodeRegular输出。首先判断shift值是否大于0,如大于0,再根据old_Low决定下一个输出bit为0或1,同时改变old_Low值。分两种情况:(1)如果old_Low前两位的值为00,10或11时可以直接输出,然后丢弃Low第一位;(2)如果old_Low前两位的值为01,将不能直接输出bit。使用bitsOutstanding寄存器来计算这种情况的连续出现次数。再根据PutBit(B)决定输出位。每一次运算shift值减1,重复运算直至shift值小于0。

2 试验及结果分析

对上述的CABAC编码器用Verilog HDL[5]硬件设计语言进行设计,在NC-Vrerilog仿真器上进行仿真实验,对H.264/AVC测试序列视频流编码测试,并与JVT校验模型JM9.6[6]的编码结果进行比较,表明该CABAC编码器可以满足实时编码的要求,且表现出色。这里使用了两个ISO/IEC标准视频测试片断“Mobile”和“Tempete”对CABAC进行测试,仿真和性能分析结果见表2、表3。

平均计算,AE耗时190个时钟编码P-slice宏块,同时耗时543个时钟编码I-slice宏块。换句话说:该算术编码器可以一个时钟处理一个位元;而且整个设计可以平均每个时钟处理0.77个位元。

对于上述设计,采用ALTERA公司的QUARTUSII5.0开发软件,表4给出了具体的实现参数。

本文提出一种高效的CABAC编码器硬件实现结构。在对H.264/AVC语法表和CABAC算法深入分析的基础上设计一种内含前馈逻辑电路三模四级流水结构算术编码器。该编码器可以一个时钟处理一个位元;整个设计综合计算平均每个时钟处理0.77个位元。但这并不是最优设计,下一步将去除取邻模块的缓冲器来减少功耗和面积,并且采用重载1-2系数的方式减少系数编码的时钟周期。

参考文献

[1] Draft ITU-T Recommendation and final draft international standard of joint video specification(ITU-T Rec.H.264|ISO/IEC 14496-10 AVC).

[2] MARPE D,SCHWARZ H,WIEGAND T.Context-based adaptive binary arithmetic coding in the H.264/AVC video compression standard.IEEE Transactions on Circuits and Systems for Video Technology,2003,(7).

[3] OSORIO R R,BRUGUERA J D.A new architecture for fast arithmetic coding in H.264 advanced video coder.Euromicro symposium on digital system design,2005.

[4] SHOJANIA H,SUDHARSANAN S.A high performance CABAC encoder.IEEE 2005 The 3rd

International IEEE-NEWCAS Conference,2005.

[5] IEEE standard hardware description language based on the verilog hardware description language(IEEE Std p1364-2001).

[6] JVT H.264/AVC Reference Software JM 9.6