摘 要: 介绍了一种基于PC+ARM+DSP+DDS体系结构的通用雷达中频信号模拟器。该系统能够模拟多种体制的雷达中频信号,而且不同信号间切换方便、使用灵活。介绍了该系统的硬件设计和在模拟相参脉冲雷达动目标信号中的应用。

关键词: 雷达中频信号模拟器 AD9852 TMS320C6416 S3C44B0X 相参

雷达信号模拟器是模拟技术与雷达技术相结合的产物。它通过模拟的方法产生雷达回波信号, 以便在实际雷达系统前端不具备的条件下对雷达系统后级进行调试[1]。随着数字技术的进步,高速、超大规模集成电路的使用,雷达信号模拟系统正朝着灵活、通用的方向发展。笔者设计了一种基于PC+ARM+DSP+DDS体系结构的通用雷达中频信号模拟器,介绍了该系统的硬件设计,并以模拟相参脉冲雷达动目标信号为例,介绍了本系统的应用。

1 系统结构设计

现代雷达信号模拟器的设计偏重于运用数字化方式实现,随着实时数字信号处理技术的发展,PC+DSP+D/A的体系结构成为雷达模拟器实现的主要方式。直接数字频率合成技术(DDS)以其在频率捷变速度、相位连续性、相对带宽、高分辨率以及集成化等方面的优异性能,成为现代频率合成技术中的佼佼者,同时也为雷达中频信号模拟的实现方式提供了新的选择[2]。

本设计采用PC+ARM+DSP+DDS的体系结构。PC机对目标及环境进行建模、运算,生成雷达中频信号仿真数据库,DSP根据模拟的雷达实时状态及目标、环境的实时特性,进行数据调度、运算和处理,最后形成控制DDS所需的调幅、调相、调频等控制字,通过DDS产生雷达中频模拟信号。

出于对模拟器通用性的考虑,PC机与DSP间的通信,希望不仅能实时改变雷达模拟信号的参数,还可以适应不同雷达体制和不同信号处理机的具体要求,方便加载新的程序。虽然通过PCI(或CPCI)能实现程序加载,并且传输速率快,但不能脱机工作,且插拔麻烦,不能用于笔记本调试。本设计采用ARM作为主控模块,控制USB接口器件和DSP的主机口,完成程序的加载和参数的实时设置。

2 硬件电路的设计与实现

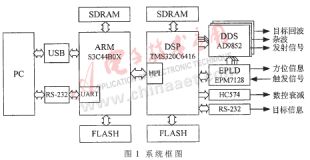

本系统主要包括以ARM为核心的主控模块,以DSP为核心的实时数据处理模块,以DDS为核心的信号生成模块,以及包括USB、RS-232和锁存器等的通信模块和电源系统,其系统框图如图1所示。

2.1 主控模块

系统主控模块负责控制和协调各种工作。ARM采用Samsung公司生产的S3C44B0X微处理器,通过集成锁相环倍频系统主频可达66MHz,最大外部存储空间256MB,片上资源丰富,外围控制能力强,性价比高[3]。由它控制USB模块接收PC机计算生成的雷达模拟信号的数据及代码,控制主机口加载DSP,控制UART实现工作状态在PC机上的实时显示。

2.2 实时数据处理模块

实时数据处理模块利用PC机生成的雷达信号模拟数据,根据设定的雷达工作状态及目标、环境的实时动态计算DDS的控制字,控制三片DDS输出雷达模拟信号。同时通过串口与信号处理机交换信息,通过锁存器向处理板提供数控衰减控制信号。

DSP采用TI公司C6000系列中的TMS320C6416,系统时钟达600MHz,数据处理速率可达4800MIPS。提供32/16bit主机口,具有两个独立的外部存储器接口,其中EMIFA支持64bit总线宽度[4]。

2.3 信号生成模块

DDS信号产生模块采用三片ADI公司生产的AD9852ASQ,它们同时生成三路中频信号。根据雷达体制和信号处理机要求不同,可分别对应不同的信号,如雷达的目标回波、杂波和发射信号,或外辐射源雷达的直达波、目标回波和多径信号,以及跟踪雷达回波信号的和支路Σ、俯仰差支路△α以及方位差支路△β等。

AD9852最高工作频率300MHz,可工作在单频、FSK、Ramped FSK、Chirp、BPSK五种模式。具有丰富的寄存器组,通过设置相应控制字可方便生成多种信号[5]。

2.3.1 总线及时序控制设计

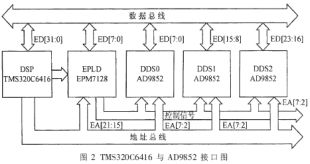

AD9852的频率、相位和幅度控制字的设置和控制信号的产生由TMS320C6416完成,AD9852可以看作是异步存储设备与TMS320C6416的EMIFA相连,EMIFA采用32bit总线。

AD9852采用并行输入,总线宽度为8位,数据传输速率可达100MHz。为了提高控制DDS的速度,本系统采用了地址总线复用、数据总线“分裂”的技术。即三片AD9852的6位地址线同时占用TMS320C6416地址总线A2~A7位,而它们的数据线分别占用TMS320C6416数据总线的D0~D7、D8~D15和D16~D23位。这样可以由DSP对三片DDS的I/O缓冲寄存器同时进行写操作,提高了总线利用率,并保证了三片AD9852输出信号的相位相参。TMS320C6416与AD9852接口示意图如图2所示。

三片AD9852的控制时序信号由EPLD产生。本设计采用ALTERRA公司生产的可编程逻辑器件EPM7128AETC100,对TMS320C6416的高位地址信号、数据信号和控制信号进行编码,产生三片AD9852全局复位、读/写使能、频率或相位切换等控制信号。

写入AD9852的数据先存入I/O缓存器,在I/O更新信号到来时写入相应的寄存器改变AD9852的工作状态。本设计中,I/O更新信号既可以由DSP写完控制字后产生,也可由EPLD将系统时钟分频定时产生,两种方式的选择以及分频倍数的控制同样由EPLD对TMS320C6416的信号编码实现。

2.3.2 时钟设计

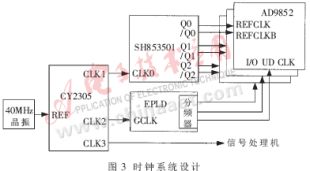

DDS输出的信号的频谱特性在很大程度上取决于参考时钟的频谱特性,参考时钟的一些主要特性如相位噪声、时钟抖动以及频率稳定度都直接地反映在DDS的输出信号上。DDS的时钟电路能否设计达到高稳定、低噪声、精确同步直接影响本系统性能的优劣。AD9852的参考时钟可以采用单端输入或差分输入,由于差分信号可以有效抑制共模噪声和电磁能量外泄,根据AD9852对峰峰值的要求(>400mV),本设计采用差分LVPECL逻辑。

本模块采用40MHz的晶振,经缓冲器CY2305输出三路同步时钟,如图3所示。其中一路接SH853501,将一路LVCMOS时钟变成三路差分LVPECL时钟后,分别传送给三片AD9852,经片上锁相环倍频形成DDS的系统时钟;一路给时序控制模块EPLD,将时钟信号分频后产生三片AD9852的I/O更新时钟;另一路作为同步时钟供给信号处理机。

2.4 通信模块

雷达模拟器与PC机间采用USB通信协议,由S3C44B0X控制USB接口器件ISP1581实现。DSP可以通过控制EPLD给信号处理机发送目标角度信息,也可以利用多通道缓冲串口向处理机传送目标信息。本系统提供了衰减控制接口,由DSP产生相应的衰减控制字,传给锁存器SN74LVC574,控制处理机上的数控衰减器。

3 相参脉冲雷达动目标信号的模拟

本系统中的三片DDS以及控制刷新和工作时序的EPLD采用同一个时钟源,并向信号处理机提供同步时钟输出,因此应用本系统可设计中频相参雷达信号的模拟。

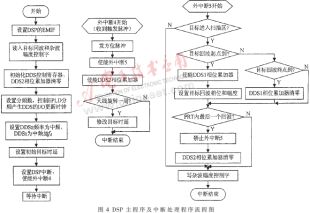

本设计中,信号处理机利用信号模拟器输出的同步时钟,将其分频生成触发脉冲,送给模拟器DSP的外中断源4,触发脉冲的周期对应雷达信号的PRT(脉冲重复周期)。EPLD分频时钟的周期对应雷达脉冲信号的脉宽,该信号提供AD9852的I/O更新时钟,同时接DSP的外中断源5。使用两路DDS。DDS1模拟动目标回波,DDS2模拟杂波信号。

在PC机上,根据要模拟的目标及环境特性,通过建立相应模型,计算生成目标回波及杂波的幅度控制字存储。DSP主程序首先将这些数据读入SDRAM。在设定的目标角度范围内,每次接收到触发信号,经由目标距离决定的延时,DSP中断产生一个目标回波信号。信号的频率和相位包含目标运动的多普勒频率信息,幅值从SDRAM读入;杂波采用DDS2连续输出产生,每隔一个脉冲持续时间DSP进入一次中断,读取SDRAM改变杂波的幅值。DSP主程序及中断处理程序流程如图4所示。

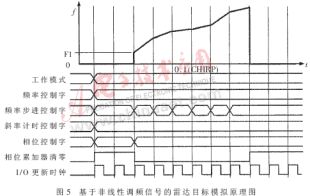

以上模拟过程采用的雷达信号为简单矩形脉冲,脉宽等于DDS更新信号的周期。如果采用大脉宽,在脉宽内每个DDS更新时钟到来时,按照巴克码或M序列改变信号的相位,可模拟相位编码脉冲压缩信号。当AD9852工作在CHIRP模式下,通过设置频率步进步长和斜率计时(即变化的频率在每个频率点上停留的时间)控制字,可模拟线形调频脉冲压缩信号。在同一模式下,若在脉宽内每个DDS更新时钟到来时改变频率步进步长或斜率计时控制字,可模拟非线性调频脉冲压缩信号,其原理如图5所示。

本设计主要具有以下特点:

(1)利用AD9852的多种工作模式,可方便产生多种雷达信号,而且频率捷变速度快,捷变时相位连续,频率分辨率高达10-6Hz。

(2)通过TMS320C6416同时控制三片DDS,读写速度快,保证了实时性和输出信号相位相参性。

(3)通过ARM控制USB模块和DSP主机口,可实时修改信号参数和加载新的程序及数据。

(4)采用三路DDS,并提供同步时钟输出,为适应不同体制雷达的要求提供了保证,更具通用性。

实验和应用结果表明,该系统能够模拟多种体制的雷达中频信号,而且不同信号间切换方便,使用灵活。该系统为雷达中频信号模拟提供了一个通用的硬件平台。在此基础上,通过丰富和完善软件数据库,可建成通用雷达中频信号模拟系统。

参考文献

1 R.L.米切尔著,陈训达译.雷达系统模拟[M].北京:科学出版社, 1982

2费元春,苏广川.宽带雷达信号产生技术[M].北京:国防工业出版社,2002

3 S3C44B0X RISC MICROPROCESSOR.SAMAUNG Electronics.2000

4 TMS320C6416 FIXED-POINT DIGITAL SIGNAL PROCES-SOR. Texas Instruments Inc. 2004

5 CMOS 300 MSPS Complete-DDS. Analog Devices Inc.1999