前言

伴随着工艺技术水平的提高,当前ASIC设计规模和设计复杂度也不断的提高。合理的选择验证工具在ASIC设计过程中起了关键作用。下面就结合实际的项目开发,对比验证工具的特点,帮助大家更好的认识验证工具。

SystemC 介绍

SystemC是一个开发硬件的面向对象的新型建模方法,建立在C++基础上,是为了方便系统级设计和IP交换。System C是一个开放的标准,由13家EDA和电子行业的公司共同控制。

包括

ARM Ltd.;Cadence Design Systems, Inc.;CoWare;Fujitsu;Mentor Graphics;Motorola;NECSynopsys

System C的源码可以从http://www.systemc.org/网站上免费下载。SystemC是由一些C++的类库

组成。用System C开发的硬件模型可以用标准的C++编译器来编译:

Unix/Solaris: bcc,gcc

Windows: MSVC

经编译后形成一个可执行的应用程序,设计人员可以通过console来观察系统的行为,验证系统功能和结构.

Specman E介绍

Specman Elite是Cadence公司的验证技术工具,它能提供可配置、可再使用和可扩展的验证组件。能够产生足够多的测试激励讯号,并能对设计行为与预期结果进行检查确认。

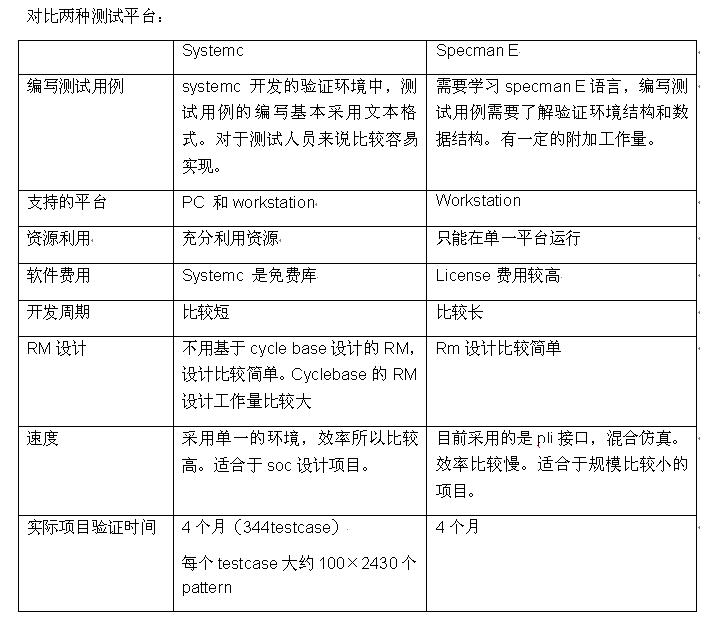

1. EOS 系统的验证

测试EOS 系统采用SystemC,比较以往的以verilog,specman E,vera语言要有以下特点, 不用付高额的eda tool 费用;可以充分的利用个人电脑系统资源;实际的开发周期大大缩短。

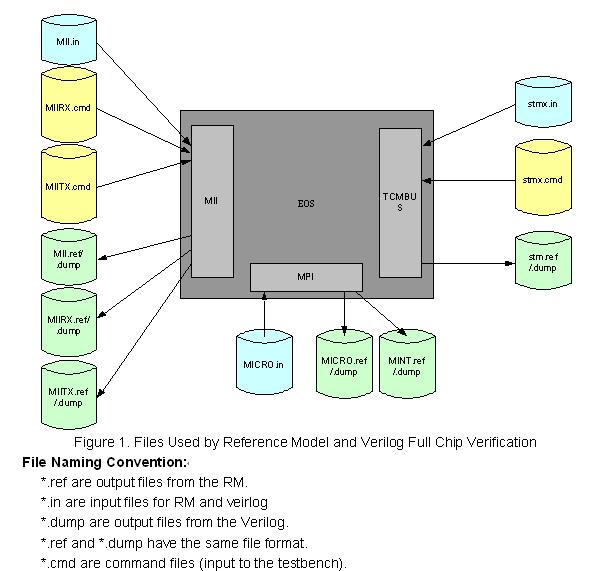

下面是EOS验证系统的设计框图。

mii: Mii Interface

MPI: Microprocessor Interface

TCM: TCMBUS Interface

RM设计和测试用例设计基于pc的c++环境开发,所有的测试用例产生的输入输出结果存为文件。Verilog代码根据输入文件产生激励,根据端口的输出产生输出文件(*.dump)。结果的检查是通过比较所有的RM输出的文件(*.REF)和verilog输出的文件(*.DUMP)。

RM设计思路,基于数据流设计,大大减少了具体硬件实现上的细节,提高了RM设计效率。

这个基于RM(reference model)设计的方法,在项目前期验证设计系统结构设计是否合理;后面验证可以继承项目前期系统结构设计阶段的成果。同时基于硬件资源环境4 workstations 和13 PC。由于PC资源充足,把测试用例的设计和RM测试在PC上进行设计。由于verilog的开发在workstation环境下,并且资源紧张,是项目开发进度的瓶颈,所以选择verilog速度最优的验证途经。

基于specmanE实现测试SDH系统软件

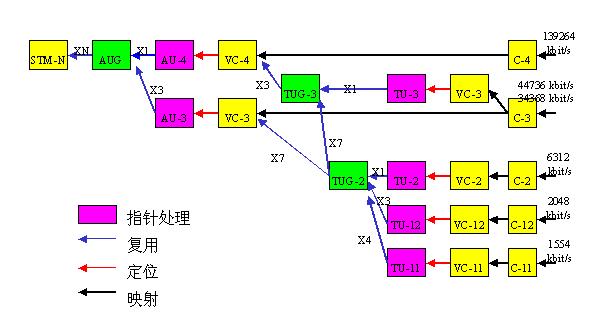

CPXXX支持的SDH业务基本复用结构如下:

根据数据结构特点和E语言特点,创建了STM4、STM1、AUG1、AU4、AU3、VC4、TUG3、TUG2、TU3、TU2、TU12、TU11、VC3、VC2、VC12、VC11、C4、C3、C2、C12和C11基本数据结构。实际的测试数据是通过扩展基本数据结构的方法配置SDH数据生成帧。可以配置数据结构包括STM4、STM1、AUG1、AU4、AU3、VC4、TUG3、TUG2、TU3、TU2、TU12、TU11、VC3、VC2、VC12、VC11、C4、C3、C2、C12、C11。配置方法的实质是对各种数据结构生成的初始化函数进行个性化扩展。

这种基于E语言的验证设计环境,可以和verilog联合仿真。但是仿真速度比较慢,单一的verilog仿真速度的1/4~1/3,在验证工作量比较大的项目中,这是个瓶颈。所以在实际的验证中,我们的策略是尽可能的把复杂的模块进行详细的模块级验证。因为每个模块功能特性不一样,这样就需要维护的验证环境比较多。

结论

1. 对于验证工具的选择,要结合资源(包括机器,人力和费用)和实际项目的特点,选择合理的有效的验证工具搭建验证环境。

2. 对于验证设计工具,不要有排斥或者崇拜的情绪,要结合实际的应用,搭建能发挥各自特点的环境是一个项目管理的要求。

参考:

1.《Writing Testbench:Functional Verification of HDL models》,Janick Bergeron, Qualis design corporation.

2.《E Reference》 Verisity Design, Inc.

作者简介: 陈思军,project manager , Chiphomer Technology Limited.