1.前言

短波发射主要用于各广播电台之间,各核潜艇之间的相互通信。发射机主要由电控逻辑装置、过荷保护装置、频率预置和自动调谐装置等组成。为了保证发射机能工作在所需的频率值,必须对高频回路进行精密调谐;原来的调谐控制单元是由大量电位器、继电器构成,采用继电器逻辑控制方式,用继电器的接点组合成逻辑功能,硬件电路多而复杂,可靠性低。

本设计采用现场可编程门阵列来完成电子系统集成化,以使整个系统达到高可靠性、高集成度、优品质、低成本、微功耗、小体积的目的,以便实现对电台的远程监控和管理。

2。系统设计

一般短波发射机具有“手动”、“预置”、“半自动”、“自动”四种调谐方式,本论文主要讨论自动调谐方式的设计。

2.1系统的组成及工作原理

自动调谐是指在调谐过程中根据当前发射机的工作频率,精确地将各个调谐元件调到与该频率相对应的过程。

整个系统有粗调、细调两部分构成, 调谐元件均为电感线圈和真空可变电容等,改变其机械转动圈数即可改变其电气参量。通过电机带动被调元件转动,即可实现被调元件的电气参量相应改变。而被调元件的位置信息是通过与该元件机械联动的跟踪电位器的中心抽头电压体现的。在EEPROM中存储有发射机在不同工作频率下多路调谐元件所对应的最佳位置信息。调谐过程为:从EPROM中取出该频率所对应的每一个调谐元件位置信息送给FPGA;FPGA同时从A/D转换器中读回各调谐元件当前所处的位置信息,将二者位置信息进行比较,由FPGA的判断逻辑按其差值的大小和极性来控制步进电机的转速和方向,直至二者的差值为零,即达到所调频率的位置。这种自动调谐方式只是粗调,对于精确定位的,还需要进行细调,细调误差信号由鉴相器和鉴阻器给出。

系统中除A/D (MAX127八路12位转换器)外,其他所有的功能都集于FPGA中。

2.2 控制单元

在本设计中调节的执行机构选择的是步进电机,步进电机的角位移量与输入脉冲严格成正比关系,具有良好的开环跟随性,没有累计误差,定位精度高、动态响应、反向快,而且通过驱动器的细分,其性能可以大幅提高。

自动调谐主控单元所采用的FPGA是FLEX10K,其拥有独特的逻辑实现结构—嵌入式阵列和逻辑阵列,每个嵌入式阵列由EABs组成,这些EABs可以非常灵活地实现ROMs、同步和异步FIFOs、双口RAM等,并可实现在线重配置。本系统采用自顶向下的设计方法,由多个具有特殊功能的逻辑宏单元构成。

主要模块如下:

(1)时钟脉冲发生器宏单元:对于输入为16MHZ的标准工作频率,通过计数方式使其16、10分频等,直至产生0.5HZ的标准时钟脉冲输出。0.5HZ—1MHZ的时钟输出以备适用于不同触发器的时钟频率。

(2)码制转换宏单元:对A/D采集的数据进行转换、送显示。

(3)工作频率检测宏单元:设计它的目的是为了检测实际工作频率是否合乎标准。通过八个计数器一秒内累计的脉冲数来检测实际高频信号的工作频率,八个计数器可检测最高几十兆的工作频率。

(4)预置位置宏单元:预置位置宏单元输出调谐元件的理论位置信息。此外,还有地址输出宏单元、步进电机正/反转宏单元和八路选择自锁宏单元等。

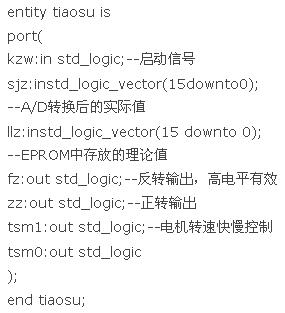

以下是步进电机控制宏单元的设计:由位置预置值与实际位置值之差来控制电机的正反转;并可以控制电机的转速(步进电机采用细分控制),如当预置值和实际值最高八位不等时,控制电机以高档速度转动;当最高八位相等而D4—D7四位不等时,控制电机以次高档速度转动,以此类推根据不同的比较结果按不同的速度进行快速的调整。其部分VHDL描述语言实现如下:

3.结束语

通过FLEX10K及高速A/D实现的自动调谐系统,可以做到自动运行、自动纪录、自动开关机、自动报警等,提高了工作效率和工作质量,并可以实现对电台的远程监控与管理,达到对电台的有效监控。