保密的重要性

对电子系统而言,FPGA的保密性极其重要。图1列出了两个系统设计的示意图,左边为1995年所作的系统设计,在该设计中,以ASIC芯片为核心,FPGA仅起到胶合逻辑的作用;在右边2005年进行的同类型系统设计中,不难发现FPGA已经成为系统设计的核心,它整合了原有ASIC及部分ASSP芯片的功能,因此FPGA作为系统芯片直接取代了ASIC的功能。随着FPGA性能、容量与功能的不断提升,今天的FPGA 已成为系统的心脏、知识产权的集合,所以如果FPGA存在安全性问题的话,与其相关的产品将遭受严重打击。

保密性定义——四个对FPGA最大的安全威胁

a.克隆

克隆是指竞争对手拷贝启动 PROM 或从

板上拦截处理器码流并进行复制。如果设计中包含外部码流时,则该设计的IP 对克隆非常脆弱。

b.反向工程

反向工程即竞争对手由重建您的设计原理图或网表复制您的设计。在这个过程中,竞争对手将了解设计的运作从而进行改进。

c.过建

过建在把您的产品交给无道德的合同制造商生产时出现,这些制造商能在开放市场上购买额外的FPGA元器件,然后在厂家没有允许的情况下,生产额外的产品,在没有开发成本和不需要提供技术支持的条件下,以更低的价格在市场上售卖,从而牟取利润。

d.拒绝服务

拒绝服务属于恶意破坏的行为,您的竞争对手或者黑客能够通过重新编程您系统上的 SRAM FPGA而使您的系统不能运行。拒绝服务使厂家的声誉、产品的质量等形象将遭到破坏。

Actel 第三代 FLASH FPGA

在了解了保密性的定义及FPGA保密重要性的基础上,Actel推出了第三代Flash FPGA,具有众多优点与特性。

Actel第三代Flash FPGA,包括两个产品系列:ProASIC3与ProASIC3E。ProASIC3能实现30k到1M的门密度,它的容量高达144kb SRAM,具有288个 I/O ;ProASIC3E能实现600k到 3M的门密度,它的容量高达504kb SRAM,具有604个I/O。

这两个系列均具备增强的高性能结构,其时钟频率最高可达350MHz,相对于第二代产品来说,其封装密度提高了20%,而逻辑利用率超过95%。SRAM的工作频率也可达到350MHz,而且每个模块中均带有硬连线的FIFO控制功能。三个锁相环(PLL)的输出频率也可达到350MHz,并且具有灵活的相位输出、延迟、分频和倍频功能。这两个系列同样支持64 位、66 MHz的PCI总线。

作为以价值为基础的FPGA,第三代产品提供了全新的功能,包括:所有器件都带有1kb片上可配置的Flash ROM及带硬连线 的AES 解密安全 ISP。上一代产品中的FPGA的保密措施在这一系列内继续保持,如片上 FlashLockTM 安全措施及针对单电压工作而在片上集成的电荷泵。最后,需要提及的是产品支持19种不同的I/O标准,包括 LVDS等。Actel第三代Flash FPGA具有竞争性的成本优势,因为Flash 技术可省去SRAM FPGA额外的成本负担。此外,Flash 技术还可以提供以下独特的性能: ·单芯片;

·高安全性;

·上电即行;

·高可靠性 / 固件错误免疫性;

·低功耗;

·高性能。

Actel FLASH FPGA的保密性特点

保密性特点

Flash FPGA的物理结构与保密性

由于Flash非挥发性的特点,所以基于Flash 架构的FPGA在一个可靠的环境下被编程以后,就不再需要一个另外的码流,因此它不会受到克隆这种攻击方式的威胁。另外,它对反向工程等入侵性攻击有高度的

抵抗性,这是因为在Flash FPGA里面的用户逻辑完全取决于Flash晶体管的内容,就算把器件解体或剥离也只能显露器件内部结构,而不是 Flash 晶体管的实际内容。由于Flash FPGA表面的一致使它受到入侵性攻击时,很难辨认其探针点。

A3P/E的保密特性

FlashLock可以保证器件上的保密设定不被随便更改 ,它包括一个对应的密钥,长度为128位,其揭露密钥所需的时间为5.4x1023年,因此十分可靠。它还包括永久FlashLock及编程文档的AES加密,其AES密钥长度为128位,而揭露此密钥所需的时间将长达149万亿年。

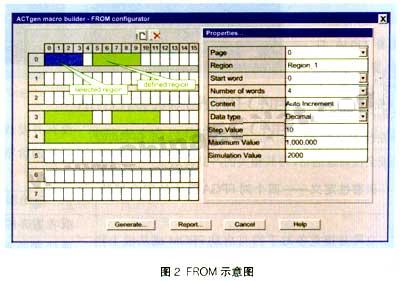

Flash ROM (FROM) 的特性及应用

第三代Flash FPGA是唯一带片上Flash ROM (FROM)的FPGA,其FROM总共有1024位,分为8个页,每页的宽度为128位,见图2。它的应用非常广泛,包括:互联网协议寻址、设备序列编码、订阅模式、系统校准设定、安全的加密匙存储、资产管理跟踪、用户喜好存储、日期标志及版本控制等。

保密性功能选项

在新FPGA上进行保密设计时,有几种不同的保密性功能选项可供选择:一、只利用FlashLock密钥进行保护 (没有AES加密),在这个选项下,用户可选择只保护FROM、只保护FPGA阵列或两者同时保护。二、AES 加密加 FlashLock 密钥保护,在这个选项下,AES 密钥一直受到FlashLock密钥保护,所以被AES加密过的文件不会包含FlashLock密钥。三、只加密 FROM、只加密FPGA阵列或两者同时加密,在这个选项下,可以独立地更新FROM及FPGA 或对其编程。编程的格式可以为纯文本格式的 STAPL 文件或经 AES加密过的STAPL文件,在这两种STAPL 文件里,可以只包括 FROM、FPGA阵列或两者同时包括。

保密报头

保密报头包含两种密钥:FlashLock密钥及AES密钥,它也包括FROM及FPGA列阵的信息认证控制。它还包括FPGA阵列与FROM的保密设定。具体的FPGA阵列保密设定包括:写入、擦除及校验的存取控制与加密/不加密的存取控制 (写入、擦除及校验);FROM的保密设定包括:写入、擦除及读取的存取控制(在此情况下校验是一直被允许的)与加密/不加密的存取控制 (写入、擦除及读取)。

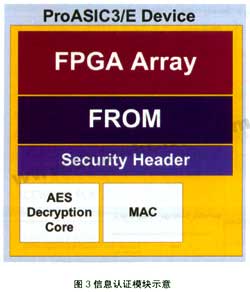

信息认证模块(MAC)

信息认证模块负责认证整个编程码流,见图3,包括AES解密核心把STAPL文件解密;MAC检查解密后的数据是否可被认识:如果正确,器件就可以被擦除及编程;如果不正确,软件会防止编程序列被启动。在认证进行过程中器件仍可正常工作。

另外该模块还负责在编程数据传进器件时检验是否存在损坏的数据,具体做法是在编程前对每个数据包进行验证。

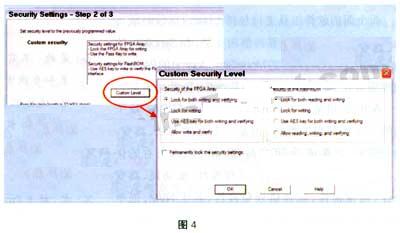

实施保密的软件设置

以下我们将介绍如何进行保密的软件设置,首先定制安全级别,如图4所示:

用户可在生成安全文件时,选择“Custom Level”选项,将弹出“Custom Security Level”对话框,即可看到FPGA阵列与FROM的保密设定选项,具体的选项包括:

——只容许在 FLASHLock 密钥正确时写入、擦除及校验;

——只容许在 FlashLock 密钥正确时写入、擦除(校验可以在没有 Fl

ashLock 密钥下进行);

——只容许在器件内有正确的AES密钥时进行写入、擦除及校验(配置器件在重编程和校验FPGA阵列时接受一个被加密的编程文件);

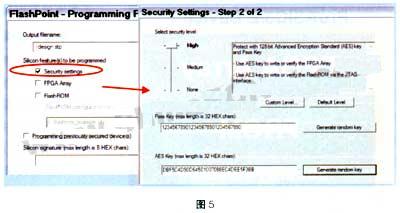

注意:a.要求在器件内有包含正确的AES密钥;b.FlashROM在这个模式下读取被禁止;c.加密过的FlashROM内容只允许进行校验。 ——接受没有FlashLock或AES密钥的纯文本STAPL 文件的写入、擦除、读取 (Flash ROM) 及校验。其次,设定保密包头,如图5所示:

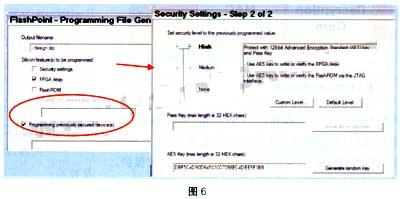

在申请编程文件时点击选择“Security Settings”选项,在弹出的对话框中选择期望的保密设定,并输入FlashLock密钥 (即软件里的Pass Key) 及AES密钥即完成了保密包头的设定。最后,编程生成加密编程文件,如图6所示。

为加密编程设定STAPL文件的具体步骤是:点击选择“Programming previously secured device(s)”选项,在弹出的对话框中点击“FPGA Array Only”或“FlashROM Only”选项,或者两者并选。最后,在弹出的“Security Settings ”对话框中的相应位置提供预编程时所用的同一个AES密钥。

完整的解决方案

为了配合ProASIC3与ProASIC3E,Actel提供了全面的硬件工具支持。新推出的低成本ISP编程器、启动工具套件(Libero Gold、FlashPro3、评估板及教程指南和文档)、可进行批量编程的Silicon Sculptor及其他调试工具,如First Silicon Solution的Logic Navigator逻辑分析器及Synplicity的Identify RTL调试器等。

而全面的软件工具支持包括:Libero 7.0(Gold 版可从网站免费下载)及业界提供的支持,如Synplicity的Synplify、Mentor Graphics的ModelSim、Magma的PALACE物理综合及WaveFormer Lite的Reactive Testbench等。

Actel公司第三代以Flash为基础的FPGA,除了高的安全性与保密性外,也是一个面向大批量生产的FPGA,它集成了ASIC与SRAM FPGA所有的优点,包括:单芯片上电即行、非挥发性、低功耗、高安全性、高保密性、固件错误免疫性、片上NVM、低单位成本、低总系统成本、无 NRE费用、可快速构建原型、快速的生产交货期及系统内可编程等诸多优点。