集成电路的发展经历了从小规模、中规模、大规模和超大规模集成的过程,但随着科学技术的发展,许多特定功能的专用集成电路(ASIC)应用日益广泛,用户迫切希望根据自身设计要求自行构造逻辑功能的数字电路。复杂可编程逻辑器件CPLD(Complex Programmable Logic Devices)顺应了这一新的需要。它能将大量逻辑功能集成于1个芯片中,其规模可达几十万或上百门以上。用CPLD开发的数字系统个有容量大、速率快、成本低的特点,且开发灵活、开发周期短。

1 器件结构和开发软件

1.1FLEX10K简介

FLEX系列可编程逻辑器件是美国Altera公司主力推出的产品。FLEX10K是该系统器件中的典型代表。与许多PLD器件一样,它有在线可配置(ISR)功能和高密度、高速度的优点;作为工业界第1个嵌入式PLD,它还采用重复可构造的CMOSSRAM工艺,把连续的快速通道互连与独特嵌入式阵列结构相结合,来完成普通门阵列的宏功能。每个FLEX10K器件还1包括个嵌入式阵列和1个逻辑阵列,能让设计人员轻松地开发集成存储器、数字信号处理器及特殊逻辑功能等强大的功能于一身的芯片。图1为其结构图。FLEX10K主要由逻辑阵列(logicarray)、嵌入式阵列(EAB)构成。其中,逻辑阵列是由多个逻辑阵列块(LAB)组成的,而每个逻辑阵列块(LAB)又包含8个逻辑单元(logicelement),在每行、列互连通道的两端都有输入/输出单元(IOE)。

1.2 MAX+PLUSII开发软件特点和设计流

用CPLD实现数字系统设计电路,关键技术是必须有一个优秀的开发软件。Altera公司的开发软件MAX+PLUS

II界面丰富,使设计灵活、方便、高效。

(1)开放的界面

MAX+PLUS II软件可与其它工业标准设计输入、综合与校验工具相连接。设计人员可以使用Altera或标准EDA设计输入工具来建立逻辑设计,对器件设计进行编译,并能使用Altera或其EDASF校验工具进行器件仿真。

(2)完全集成化的环境

它是一个完全集成化、易学易用的可编程逻辑设计环境,设计输入方式有图形输入、文本输入、波形输入、状态机设计输入。其编译及设计处理写仿真、定时分析、逻辑综合与适配均为Windows图形界面。

(3)支持各种硬件描述语言

支持各种HDL设计输入选项,包括VHDL、VerilogHDL、ABEL、AHDL等硬件描述语言。

(4)丰富的设计库

提供丰富的库单元设计调用,包括74系列的全部器件和多种特殊的逻辑宏功能、新型的参数化兆功能。对于复杂的大系统,设计者需调用宏单元库,并对其修改某些参数,而无需自己用基本逻辑单元来构成某种功能,以大大减轻设计人员的工作量,缩短设计周期。

电路的设计流程如图2所示。将所设计的电路用原理图输入和硬件描述语言输入,应用EDA软件平台(MAX+PLUS II)编译通过后,再进行逻辑功能仿零点,生成目标文件,下载到FLEX10K芯片,完成系统设计。

2 交通控制系统设计

2.1 系统介绍

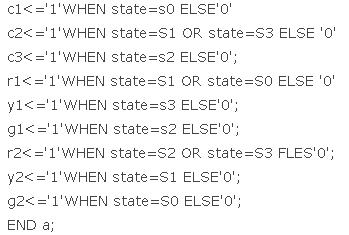

图3为一十字路口交通管理器,控制甲、乙2道的红、黄、绿3色灯。计数显示部分为2个倒计时器,显示甲、乙车道允许通车时间,指挥车辆和行人安全通行。其R1、Y1、G1为甲道红、黄、绿灯;R2、Y2、G2为乙道红、黄、绿灯。

甲道通告时间为t3,乙道通行时间为t2,黄灯亮(停车)时间为t1,C1、C2、C3为定时器工作使能信号,为1时定时器计数;W1、W2、W3为定时器的指示信号,计数时信号为0,计数结束时信号为1。

2.2 FLEX10K内部逻辑功能设计

交通控制系统芯片内部逻辑功能设计采用自顶向下的设计方法,系统顶层电路如图4所示。它分为5个次级模块:控制器(traffic_control)、定时器1、定时器2、定时器3、(其定时时间为t3、t2和t1)、计数显示(含减法计数器和动态扫描电路)。

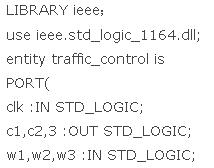

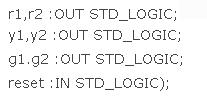

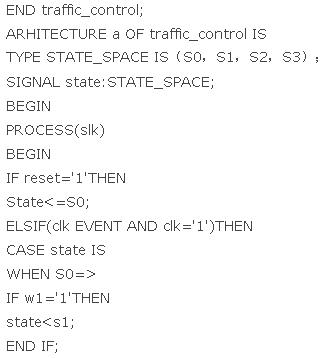

顶层电路图中减法计数器和动态扫描电路用图形输入描述,其它次级模块控制器、定时器1、定时器2、定时器3用VHDL硬件语言描述。核心模块控制器的VHDL源文件如下:

3 功能编译、设计仿真与硬件下载

本系统采用Altera公司生产的FLEX10K系列的CPLD芯片,应用该公司的MAX+PLUS II开发软件完成设计后,需对各种源文件从低层到顶层逐个编译,再进行逻辑仿真。选择器件后,打开检查项目中所有设计文件,通过检测发发现在编程器件中可能存在的可靠性不好的逻辑器件引脚分配。

Altera公司推荐的编译器可自动为项目进行引脚分配,也可人工调整引脚。在编译器窗口选择Start按钮,将对所有设计的项目进行处理,出现错误将给出具体错误提示。为了保证设计的正确性,在编译通过后,还需进行逻辑仿真。仿真通过后再应用MAX+PLUS II的编程器对所选可编程逻辑器件下载编程,便完成了交通控制系统的ASIC芯片设计和硬件固化。若在芯片外围接入必要电源、脉冲信号、显示器和指示灯,便构成了一个完整交通控制系统。它具有工作稳定、体积小、在线修改方便等特点。