基于闪存的星载大容量存储器的研究和实现

2008-08-28

作者:高怡祯

摘 要: 就闪存应用于星载大容量" title="大容量">大容量存储器时的写入速度慢、存在无效块等关键问题探讨了可行性解决方案,并在方案讨论的基础上论述了一个基于闪存的大容量存储器的演示样机的实现。

关键词: 闪速存储器 固态记录器 并行 流水线 无效块

空间飞行器的数据记录设备是卫星上的关键设备之一。自20世纪90年代初起,各航天大国开始研制固态记录器(Solid State Recorder,简称SSR)。由于SSR使用半导体存储芯片作为存储介质,所以其存储密度高、无转动部件、可靠性高、体积小、重量轻,因而逐渐成为空间飞行器的数据记录器的主流方案。闪速存储器(简称闪存)作为一种新兴的半导体存储器件,以其独有的特点得到了迅猛的发展,其主要特点有:(1)具有非易失性,掉电时数据不丢失,可靠性高;(2)功耗小,不加电的情况下可长期保持数据信息;(3)寿命长,可以在在线工作情况下进行写入和擦除,标准擦写次数可达十万次;(4)密度大、成本低,存储单元由一个晶体管构成,具有很高的容量密度,且价格也在不断降低;(5)适应恶劣的空间环境,具有抗震动、抗冲击、温度适应范围宽等特点。由于闪存的这些特点,使它受到了航天领域研究人员的关注。20世纪90年代中期,Firechild公司就曾为F-16侦察星成功设计了SSR[2],使用的主要存储芯片就是闪存;国内的FY-2卫星也曾采用闪存作为该星的固态存储器的存储介质。虽然有这些成功的应用案例,但是闪存也存在一些明显的缺点,如写入速度较慢、使用过程中会出现无效块等。本文将探讨如何解决和突破这些缺点,并依此给出一个具体的系统实现方案" title="实现方案">实现方案。

1 闪存构成星载大容量存储器的关键问题

1.1 写入速度问题

目前闪存有多种技术架构,其中以NOR技术和NAND技术为主流技术[3]。NOR型闪存是随机存取的设备,适用于代码存储;NAND型闪存是线性存取的设备,适用于大容量数据存储[4]。NAND型闪存有一定的工业标准,具有一些统一的特点,现以三星公司的K9K1G08U0M型芯片为例进行介绍。该芯片容量为1Gbit,由8192个块组成,每块又由32个页组成,一页有(512+16)×8bit,该片的8位I/O总线是命令、地址、数据复用的。读写操作均以页为单位,擦除操作则以块为单位,写入每页的典型时间为200μs[4],平均每写一个字节约需400ns,即约20Mb/s。这样的写入(编程)速度对于要求高速的应用场合来讲是难以满足的,因此必须采取一定的技术措施。

1.1.1 并行总线技术

并行总线技术亦称宽带总线技术,即通过拓宽数据总线的带宽实现数据宏观上的并行操作。比如,由四片K9K1G08U0M型闪存芯片" title="闪存芯片">闪存芯片组成一个32位宽的闪存子模块,它们共用相同的控制信号" title="控制信号">控制信号,包括片选信号、读写信号、芯片内部地址等。子模块总是被看做一个整体而进行相同的操作,只是数据加载" title="加载">加载的时候是不同的数据。这样,数据量将是使用单独一块芯片时的4倍,所以理论上速度也将是非并行时的4倍。

1.1.2 流水线技术

借鉴现今高性能计算机中的流水线操作原理,可在时间片上实现微观并行。针对闪存的写入速度慢的问题,可以对其进行流水处理。K9K1G08U0M型闪存的写入操作可分为三个步骤:(1)加载操作,即完成命令、地址和数据的载入工作;(2)自动编程操作,即由闪存芯片自动完成编程操作,将载入到页寄存器的数据写到内部存储单元的;(3)检测操作,即在自动编程结束后检测写入的数据是否正确。如果不正确,需要重新编程;如果正确,继续下一步的操作。写流水原理图如图1所示。由图1可以看到,流水线运行起来后,在任一时间片上总有若干小操作在同时进行,即在时间片上实现了复用,因此从整体上看速度将会提高。

1.2 无效块的管理

三星闪存芯片在使用过程中会出现无效块。无效块是指一个块中存在一个或多个无效位,其可靠性不能得到保证,必须加以标识和旁路(当然无效块不会影响到其它块的有效性)[4]并进行数据备份。为了对无效块实现管理,可以建立一张无效块到冗余区有效块的映射表。映射表结构如图2所示。映射原理如下: 开始是一张初始无效块映射表,这张表可以根据三星公司技术手册给出的算法建立起来。按照图示的映射数据结构对整个存储区进行编号,并根据这个编号对映射表进行排序。进行写操作时,按照上述的映射结构将写地址与映射表进行比较,比较到块级即可。如果是无效块,将待写入的数据写到被映射到的块;如果不是,则直接写入该块。如果在写某块的某页时出现编程错误,则将该块添加进无效块映射表(当编程出错时就表明出错页对应的块无效),同时从该出错页开始,将该块后面的页数据都写入到对应的映射块。这样,在数据读出时,可将读地址与映射表比较,并且需要比较到页级以确定每一页的确切存放位置。如果该页编程正确,则直接读出;如果错误,则到被映射的块的对应页读数据,并且该页之后的页也从被映射块中读数据。根据三星的技术资料,对无效块进行读操作是允许的,即对于编程出错页前面的那些编程正确的页是可以正确读出的,而对无效块进行编程和擦除的操作是不推荐的,因为有时这些操作会使邻近的块也失效[4]。所以读操作要查找到每一页的对应存放位置,而写操作只要查找到块就行。查找时采用二分查找算法。擦除完后,将擦除出错的块也添加进无效块映射表。无效块映射表需要不断维护和更新。

2 闪存构成星载大容量存储器的系统实现方案

2.1 系统的组成

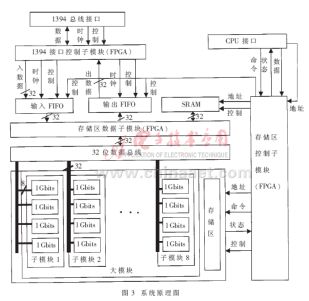

该实现方案将上述关键问题的解决方法融合进来,系统由存储区模块、接口模块、数据缓冲模块及主控模块四部分组成,系统原理图如图3所示。

2.1.1 存储区模块

为了实现并行和流水技术,整个存储区模块按如下方式构成:由4片K9K1G08U0M型三星闪存芯片组成一个子模块,8个子模块组成8级流水的大模块,而这个大模块即是整个存储区,其总容量为32Gbit。无效块备份的冗余区可以设在每个子模块内部,即从子模块的每块芯片中预留出一部分空间。这种模块化管理的方式既便于系统扩展,又可以在不影响系统正常工作的情况下旁路已损坏的存储块。

2.1.2 接口模块

系统与外部的接口有两个。一是与CPU的接口,主要完成系统的初始化、外部命令和地址的输入以及内部状态参数的输出,同时CPU 还要对存储区完成管理:无效块的管理、地址的译码和映射等;二是与外部高速数据源的接口,主要完成外部高速数据的接收和发送。这里选用了1394高速总线作为数据源总线。

2.1.3 数据缓冲模块

这一模块包括数据输入FIFO、数据输出FIFO和一个作为数据备份的SRAM。由于闪存的写入速度比较慢,如果没有数据缓冲区,外部的高速数据很有可能会丢失,而且数据回放时也需要一个缓冲区使内外的数据率匹配。考虑到编程出错时需要重新加载数据,按照流水线的工作方式,如果不进行数据备份,可能会出现出错时的数据丢失,因此选用了一个SRAM进行数据备份。当将输入FIFO的数据写入FLASH时,同时也将数据写入到SRAM进行备份;当需要重新编程时,再从SRAM中将相应的备份数据重新写入FLASH。

2.1.4 主控模块

这一模块完成整个存储器系统的内部控制,是核心控制机构,连接着存储区、数据缓冲以及外部接口三个模块,完成它们之间的数据、命令、地址、状态的相互传递、转换和处理。主控模块又分为三个子模块,即存储区控制子模块、存储区数据子模块和1394接口控制子模块,分别由三片FPGA(现场可编程逻辑阵列)完成。

3 系统的基本工作原理

下面以闪存的写(编程)操作为线索,阐述系统的基本工作原理。

3.1 写操作的准备和启动

1394高速总线上的串行数据通过一定的接口芯片变换成并行数据。当大容量存储器接收到外部1394高速总线上的数据存储握手信号时,1394接口控制子模块利用握手信号产生一定的时钟和控制信号,控制高速数据缓存入32位的输入FIFO。当输入FIFO的存储量达到一次8级流水运行的数据量时,就向CPU发出中断,申请写操作启动。

3.2 写流水操作的加载和自动编程

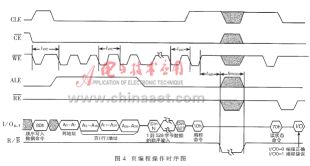

存储区的寻址采用内存寻址方式,即为FLASH存储区分配一段内存空间,CPU象访问内存一样对其进行寻址,大小为2M,共21根地址线,其中高3位是子模块选择,选择8级流水中的某一级;低18位是子模块的每块芯片的页(行)地址。对于芯片内的列地址,由于向每一页写入数据时,总是从页的起始处开始写,即列地址(页内编程起始地址)是固定的,因此可以直接由FPGA给出。当CPU接收到写操作启动的中断申请时,给出写操作命令,并进行地址译码。存储区控制子模块将CPU给出的命令和地址经过一定的逻辑转换成片选、命令、地址及控制信号,依次对8级存储子模块进行片选并完成各级命令和内部地址的加载工作。然后再由存储区控制子模块产生一定的控制信号,控制输入FIFO启动对8级存储子模块的数据加载工作:首先对第一级进行片选,数据流由输入FIFO经存储区数据子模块驱动后输入第一级存储子模块,经过512个写周期后(页有效数据),完成对四片并行的FLASH芯片的页加载,加载完成后由存储区控制子模块给出自动编程的起始指令10H,第一级子模块的四片芯片就开始将加载到页寄存器的数据写入到芯片内部,进行自动编程工作。页编程操作时序图如图4所示,这时它们的片选可以无效。然后使第二级片选信号有效,开始对第二级进行数据加载。依次下去,完成8级存储子模块的数据加载。

3.3 检验写流水操作是否成功

第一级存储子模块在完成了数据加载后开始自动编程,待到8级的数据加载都完成后,其自动编程已接近尾声。此时不断检测该级四片芯片的忙/闲端口,一旦它们都处于“闲”状态时,说明自动编程都已经结束。这时由存储区控制子模块的控制逻辑产生片选信号,选通第一级存储子模块并发读状态命令70H,通过采样四片芯片的I/O端口的“0”状态来检测编程是否成功,并将检测结果锁存进FPGA内部的寄存器;然后按同样的方式对第二级存储子模块进行检测,依次下去,直到“记录”下8级存储子模块的编程成功与否的状态信息后,向CPU申请中断并将这些状态值返回给CPU。CPU则根据这些状态值更新无效块映射表,并将无效块映射到冗余区,对编程出错的存储子模块重新编程。重新编程与正常编程的工作原理是一致的, 只不过数据是由SRAM输出给FLASH,且不能进行流水操作。

4 采用并行及流水技术后速率的估算

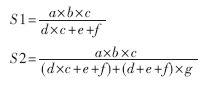

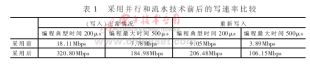

根据上述实现方案以及三星闪存芯片的时序和各项性能指标参数,可以对采用四片并行和8级流水技术后的写速率做一个理论上的大致估算,整个流水操作完成所需的时间应以最后一级流水完成的时间为准。估算方法如下:令FLASH芯片中一页的数据量为a, 并行操作的芯片数为b, 流水的总级数为c,命令、地址和数据的加载时间为d, 芯片自动编程时间为e,检测时间为f,需重新编程的级数为g,正常写速率为S1,重新写入时的写速率为S2,则:

采用并行和流水技术前后的写速率比较如表1所示。可以看出,采用该方案后的速率较采用前有了大幅度的提高。即使考虑到硬软件的延迟及其它一些因素,这个速率的提升仍然是可观的,说明这个设计方案是可行的。

随着空间技术的不断进步,要求空间飞行器上的大容量存储器件朝着更大容量、更高速度、更低功耗、更小的重量和体积、更合理有效的存储区管理以及更高可靠性的方向发展。从商业领域发展而来的闪存,存储密度大、功耗小、可靠性高、体积小、重量轻且成本也在不断降低。对于其写入速度慢及存在无效块等主要缺点,可以通过其自身工艺技术的不断发展及融合其它领域的思想和技术,如本文所述的并行技术、流水线技术等得到解决,因而有着良好的应用前景。

参考文献

1 崔 刚.FLASH MEMORY(快速擦写存储器)在航天计算机中的应用.电子计算机外部设备, 1995;19(3)

2 Fishell, Wallace G. High-speed Solid State Recorder for Airborne Recce. SPIE; 2829,Airborne Reconnaissance,1996 3 李 力. 闪速存储器技术现状及发展趋势.单片机与嵌入式系统应用, 2001(8)

4 三星闪存数据手册和常见问题解答.http://www.samsungelectronics.com/semiconductors/flash